Schottky junction tunneling field effect transistor

A technology of tunneling field effect and Schottky junction, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., to achieve the effects of suppressing short channel effects, reducing electric field strength, and increasing width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be described in detail below in conjunction with the accompanying drawings.

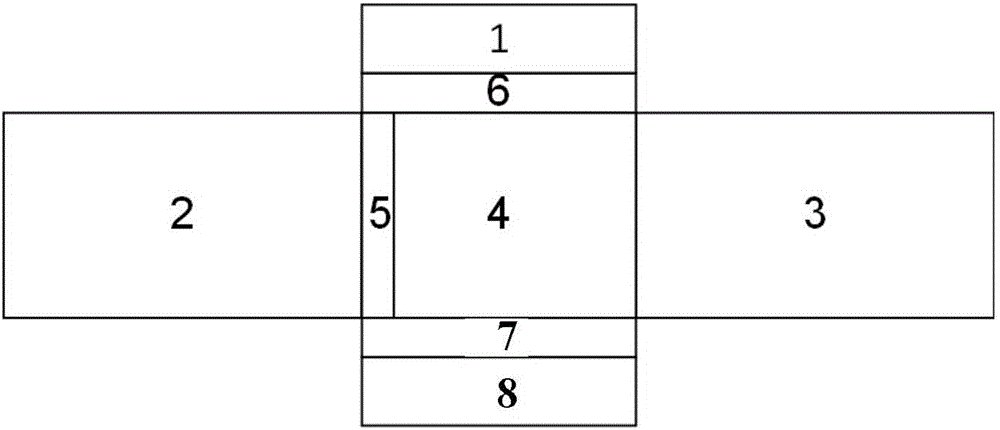

[0016] Such as figure 1 A Schottky junction tunneling field effect transistor is shown, comprising a first gate 1, a source region 2, a drain region 3, a channel region 4, a heavily doped pocket region 5, a first gate dielectric layer 6, a second A gate 8 and a second gate dielectric layer 7; wherein the upper and lower sides of the channel region 4 are respectively provided with a first gate dielectric layer 6 and a second gate dielectric layer 7; above the first gate dielectric layer 6 is provided with a first gate 1. A second gate 8 is provided under the second gate dielectric layer 7; the first gate 1, the first gate dielectric layer 6, the second gate 8 and the second gate dielectric layer 7 maintain vertical symmetry; the source region 2 and The drain region 3 is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com