Controllable dynamic multi-thread method and processor

A processor and multi-thread technology, applied in the direction of electrical digital data processing, instruments, machine execution devices, etc., can solve the problems of increased processor power consumption and hardware complexity, and achieve the effect of reducing power consumption and improving utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] Below in conjunction with accompanying drawing, technical scheme of the present invention is described in further detail:

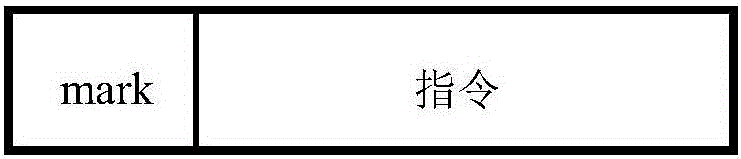

[0061] The present invention adds a set of symbols (marks) corresponding to the instruction thread identity and its priority information in the instruction system of a processor adopting a multi-stage pipeline structure. The instruction system of the processor obtains the mark of the thread identity and its priority information while reading (Fetch) the instruction. The instructions of the processor control the computing system (Branch) to arrange the hardware resources of the processor and the execution sequence according to the information of the mark. This mark will always follow each step of the instruction execution to track the execution steps of the instruction, and indicate the dependency of the instruction and the instructions / data before and after it and the order of priority execution according to the priority information.

[0062] The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com