Wafer processing method

一种加工方法、晶片的技术,应用在金属加工设备、制造工具、适用于磨削工件平面的机床等方向,能够解决粘接膜破碎、飞散器件芯片品质、器件芯片品质降低等问题,达到抑制间隙的扩展、减少侧面污染、抑制移动的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Hereinafter, preferred embodiments of the wafer processing method of the present invention will be described in detail with reference to the drawings.

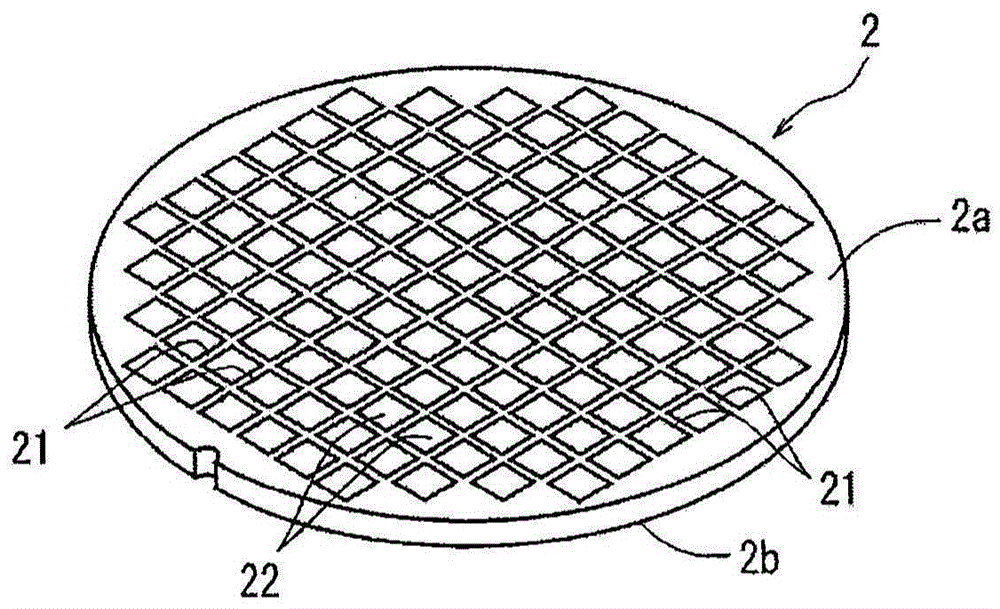

[0033] figure 1 A perspective view of a semiconductor wafer processed according to the invention is shown in . figure 1 The illustrated semiconductor wafer 2 is composed of a silicon wafer with a thickness of, for example, 500 μm. On the front surface 2 a, a plurality of planned dividing lines 21 are formed in a grid pattern, and are formed in a plurality of regions divided by the plurality of planned dividing lines 21 . There are devices 22 such as ICs and LSIs. Hereinafter, a wafer processing method for dividing the semiconductor wafer 2 into individual devices 22 along the planned dividing lines 21 will be described.

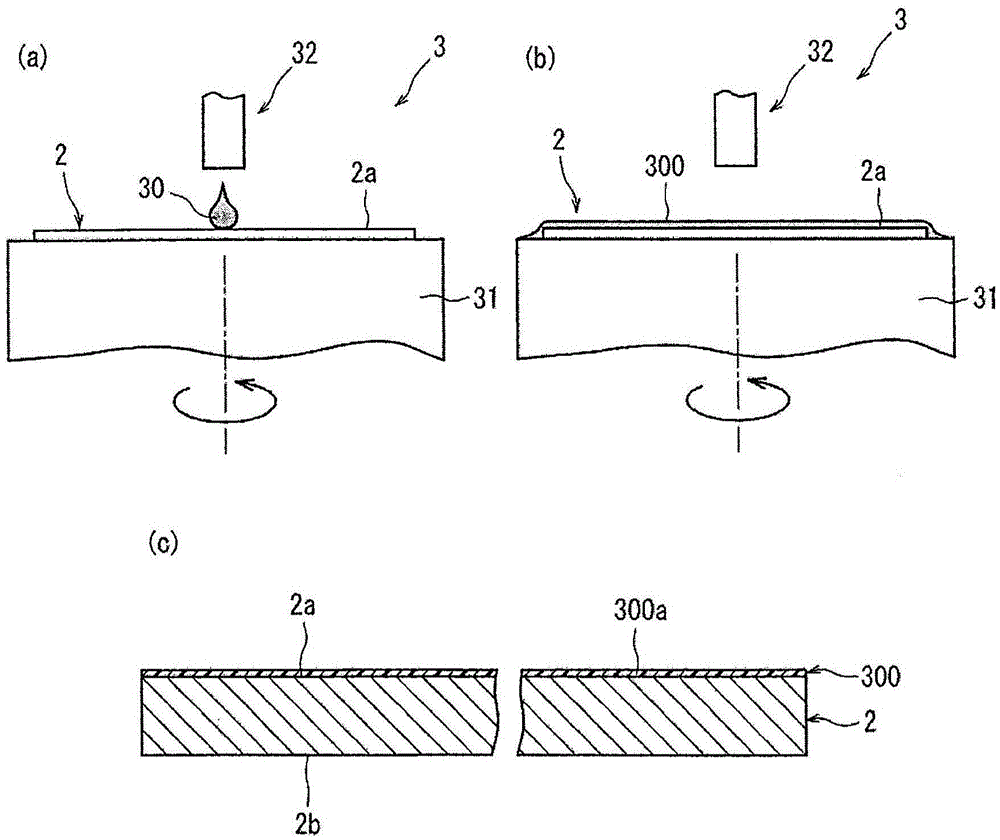

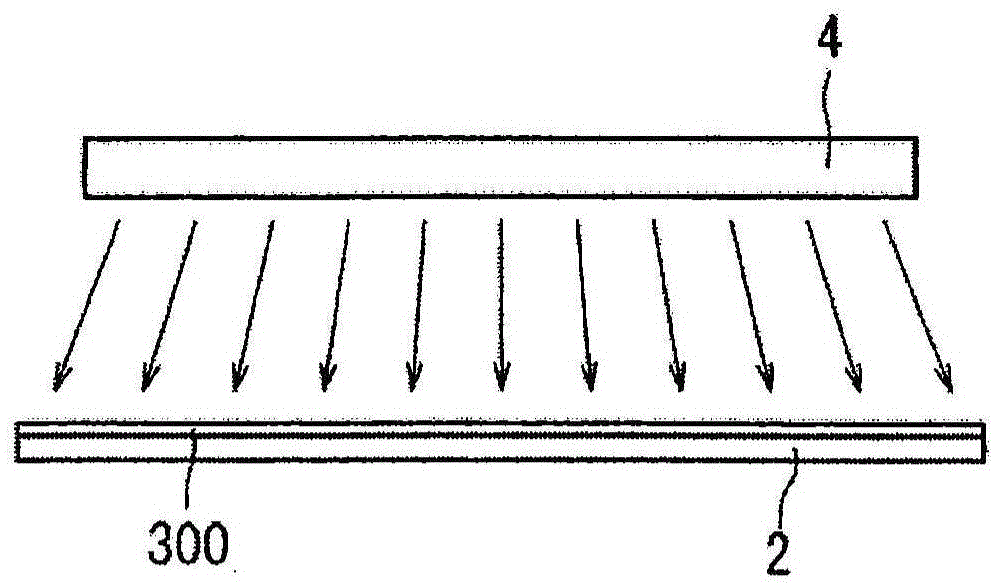

[0034] First, a protective film forming step is performed to form a protective film by coating the front surface 2 a of the semiconductor wafer 2 with a liquid resin that is hardened by irradiation o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com