Bus communication receiver decoding circuit

A decoding circuit and bus communication technology, applied in the field of bus communication and bus communication receiving end decoding circuit, can solve the problems of slow charging and discharging speed, fast charging and discharging speed, increased cost, etc., to achieve stable voltage, good charging and discharging current, good charging and discharging control effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to describe the technical content of the present invention more clearly, further description will be given below in conjunction with specific embodiments.

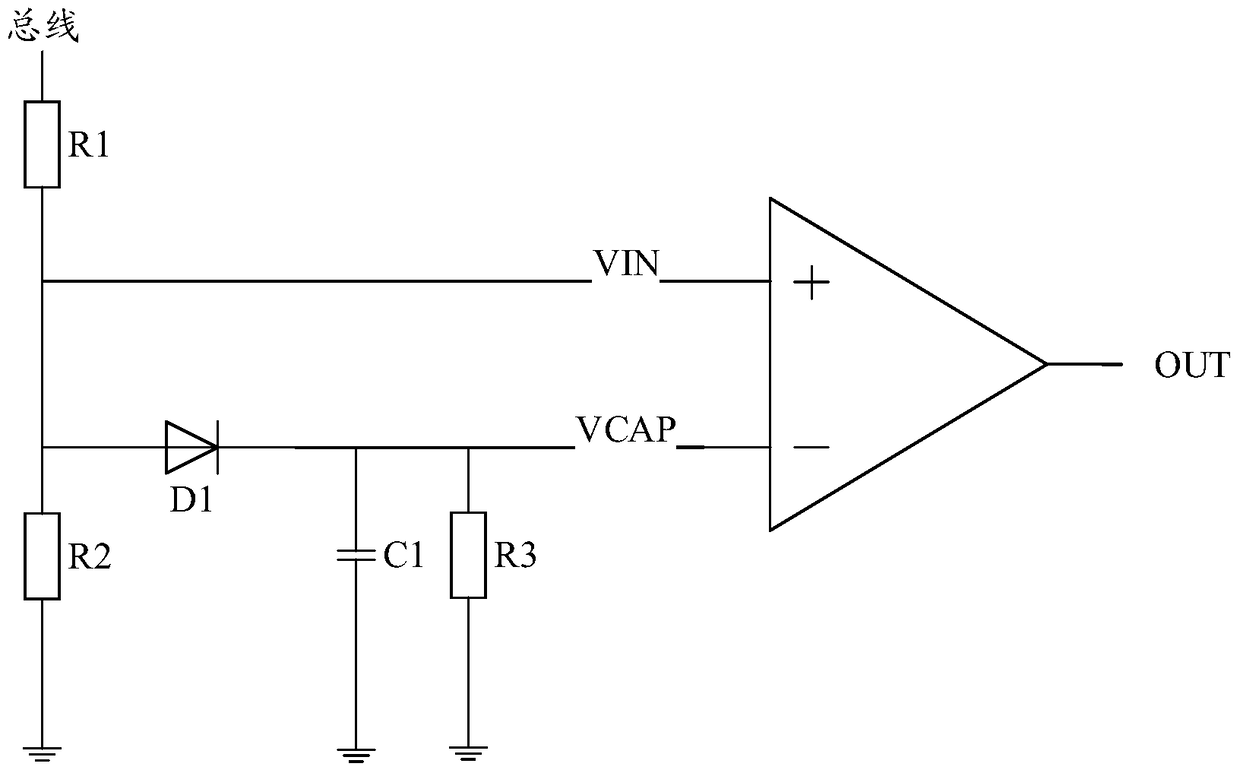

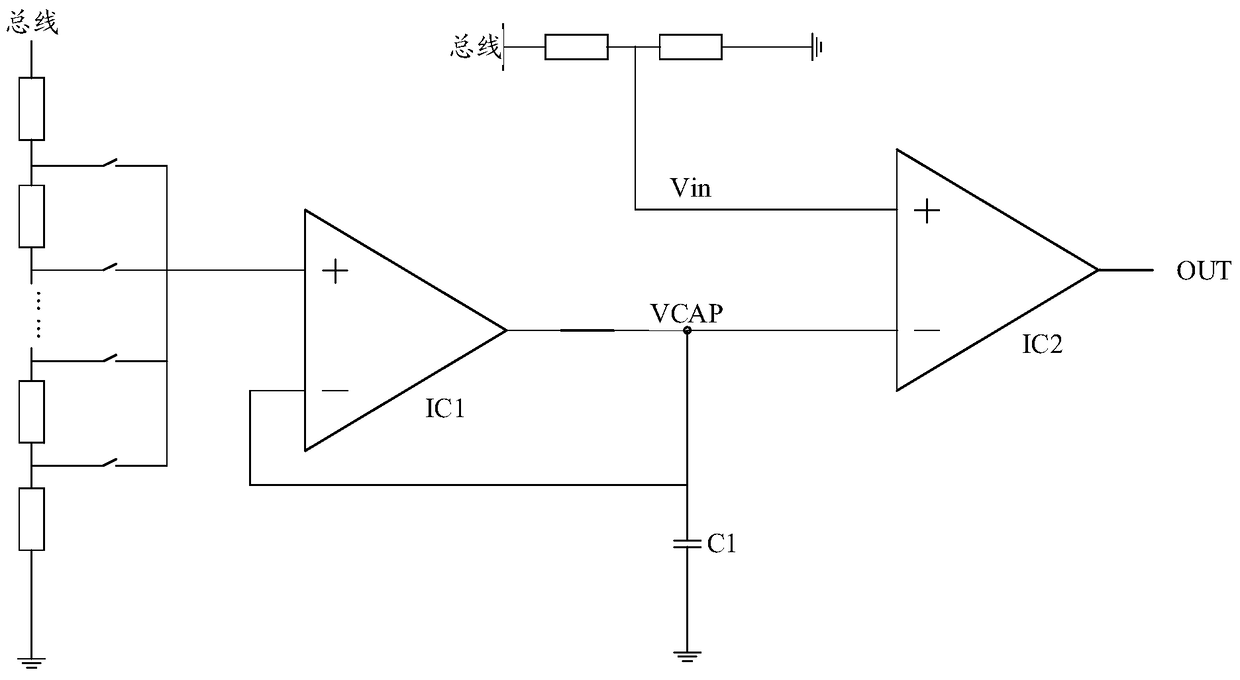

[0034] The present invention adopts the method of relative percentage comparison, which eliminates the differences caused by the different lengths of the connecting wires between the slaves closest to and farthest from the master, and also makes each slave use the same setting value to avoid different different slaves use different settings.

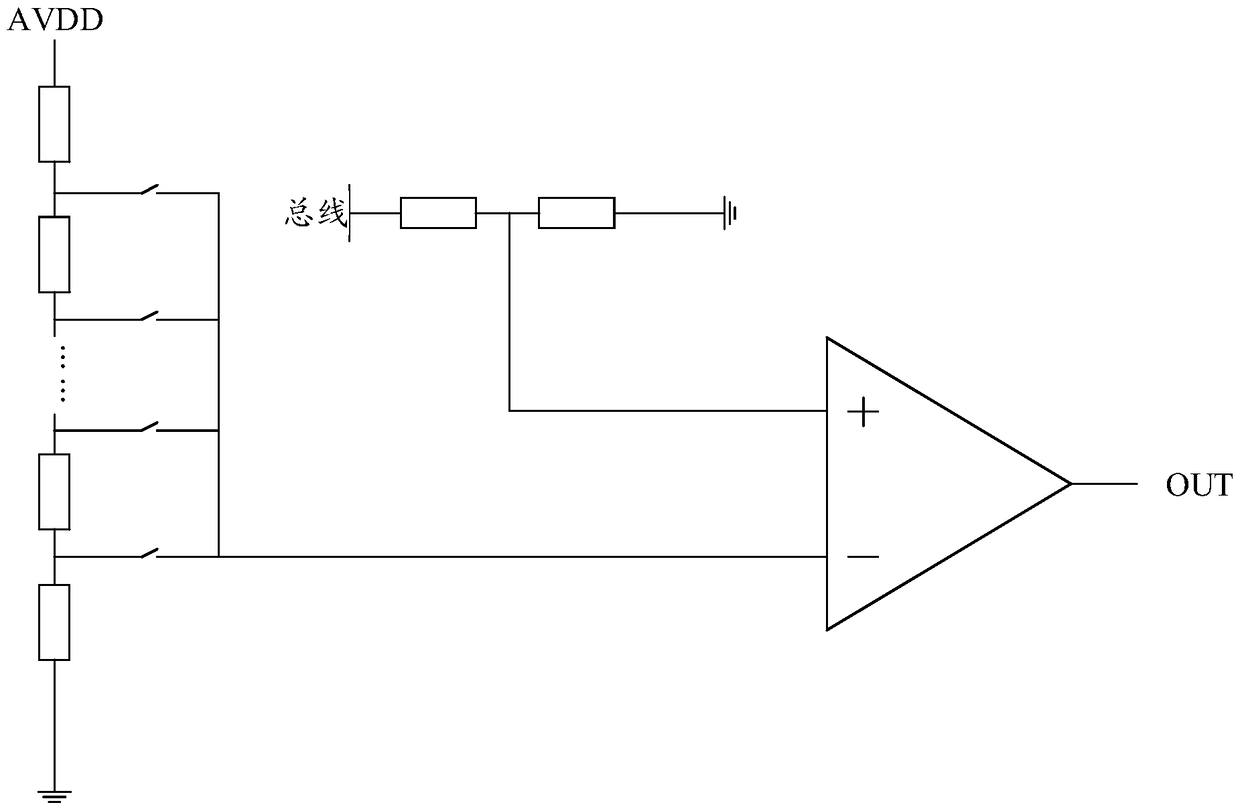

[0035] The bus communication receiver decoding circuit of the present invention includes: a first bus voltage divider module, which is used to input the divided voltage generated after the bus voltage is stepped down to the positive input terminal of the first comparator; a threshold voltage generation module , used to generate a threshold voltage according to the bus voltage, and the threshold voltage is input to the inverting input terminal of the first comparator; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com