Method for monitoring fuse burning yield rate in chip test

A technology of chip testing and fuse burning, which is applied in semiconductor/solid-state device testing/measurement, electrical components, circuits, etc., can solve problems such as test product loss, and achieve the effect of avoiding irreversible loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with specific drawings and embodiments.

[0025] In this embodiment, the method for monitoring the achievement rate of burning the fuse in the chip test includes the following steps:

[0026] Step S1, establish a fuse truth table, as shown in the following table;

[0027]

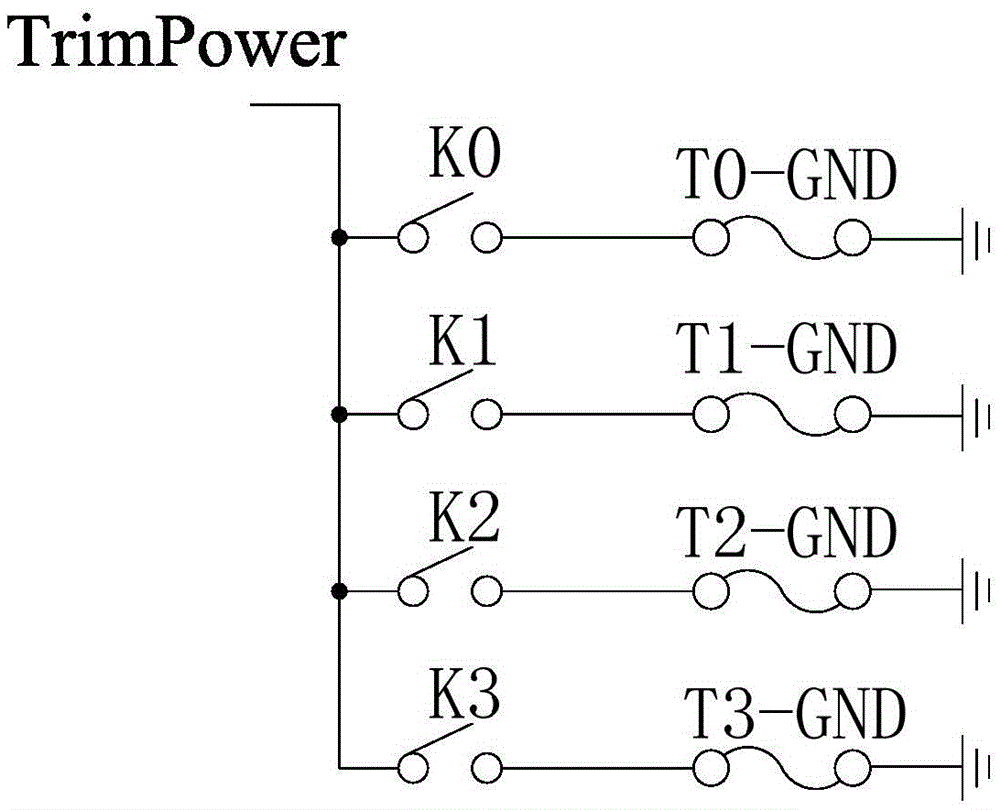

[0028] In this example, the number of fuses is four sections. After a certain section of fuse is blown, the change in the reference voltage of the chip has been specified in advance during the fuse design process. In this example, the changes in the reference voltage after each section of fuse is blown are respectively : -12.5mV(T3-GND), -25mV(T2-GND), -50mV(T1-GND), +100mV(T0-GND); T0-GND, T1-GND, T2-GND, T3-GND represent Four section fuse;

[0029] The fuse truth table has a minimum reference value of 500mv and a maximum reference value of 700mv; the fuse truth table also has a reference voltage standard value of 600mv; If t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com