Digital circuit design method and related system

A technology of digital circuits and design methods, applied in the fields of electrical digital data processing, computing, special data processing applications, etc., can solve the problems of circuit program files that cannot be matched with simulation, no errors are found, difficulties, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

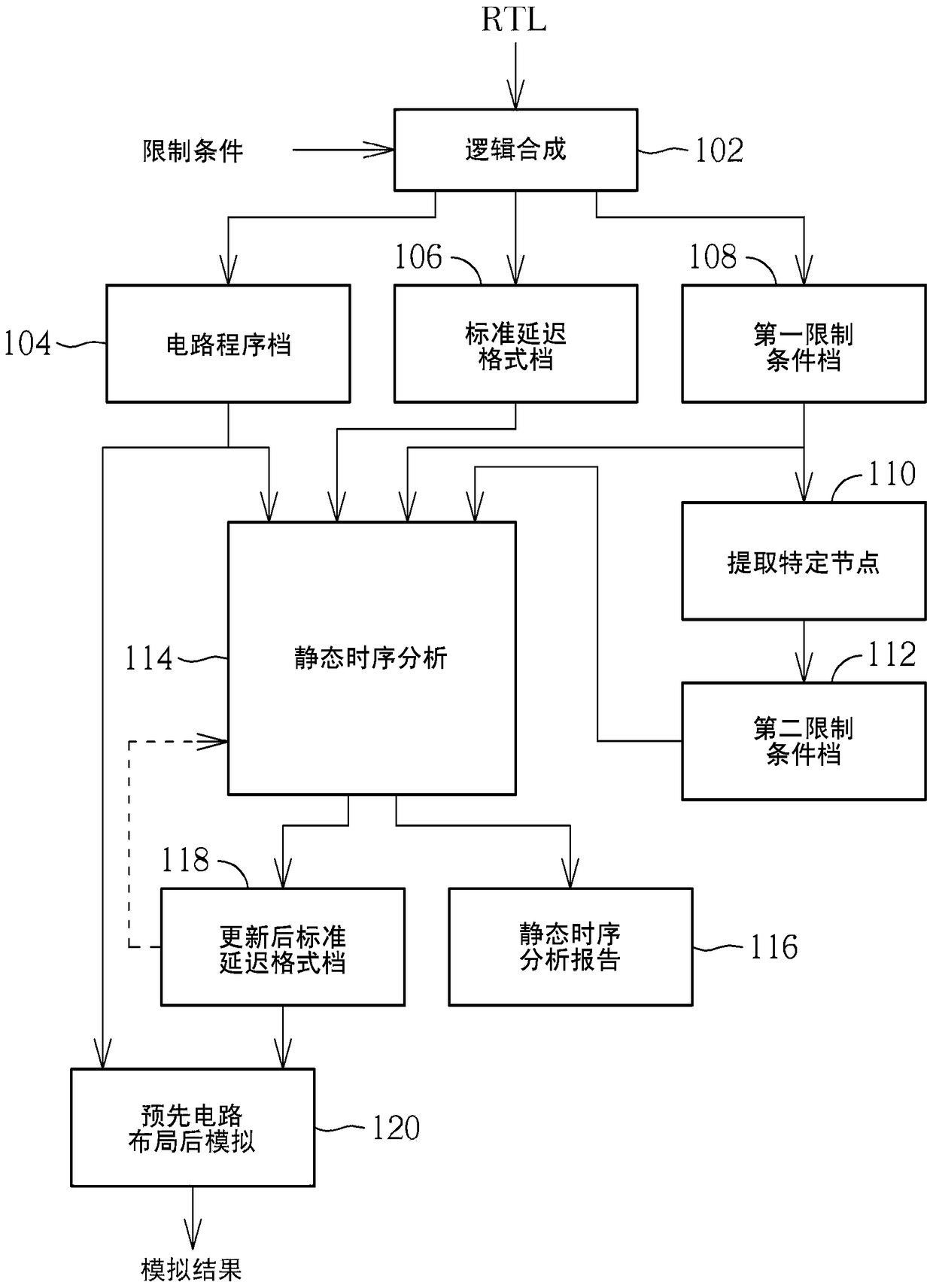

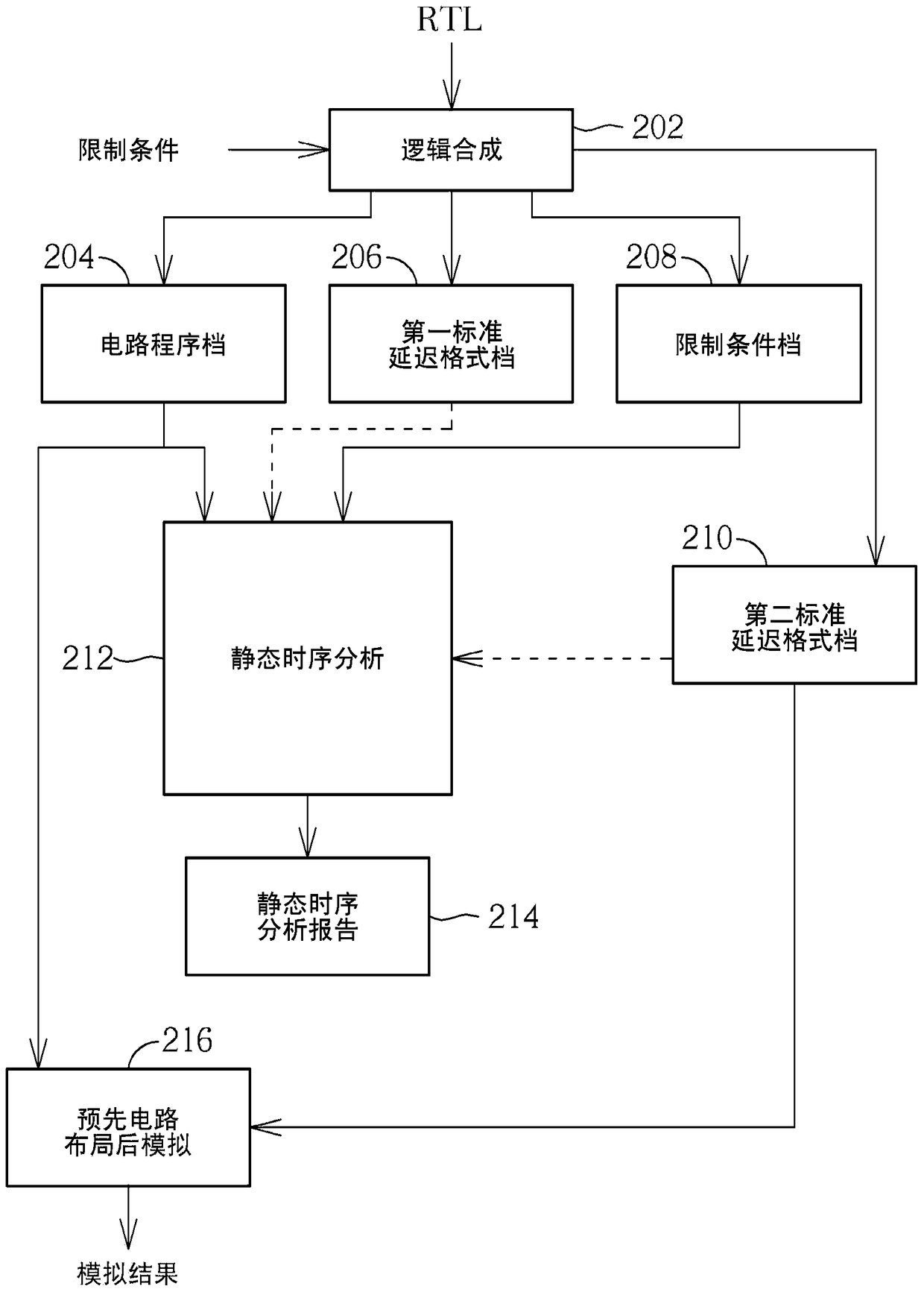

[0015] Please refer to figure 1 , figure 1 It is a flowchart of a digital circuit design method according to an embodiment of the present invention. In this embodiment, the digital circuit design method is executed by a plurality of program instruction modules after a system for digital circuit design is loaded into a computer / processor, refer to figure 1 , the flow of the digital circuit design method is described as follows.

[0016] First, in step 102, a logic synthesis (logic synthesis) operation is performed according to a Register Transfer Level (RTL) design and a plurality of constraints, so as to generate a circuit in steps 104, 106, and 108 A program file (netlist), a standard delay format file (Standard Delay Format, SDF), and a first constraint file (constraint file). The above constraints are input by the engineer, and mainly include which pin is the clock input point, and what is the frequency of the clock...etc.; the circuit program file is a file format descr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com