Cache consistency test method

A test method and consistency technology, applied in the use of remote testing to detect faulty hardware, error detection/correction, and detection of faulty computer hardware, etc., can solve problems such as difficult traversal and multiple cache consistency scenarios.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

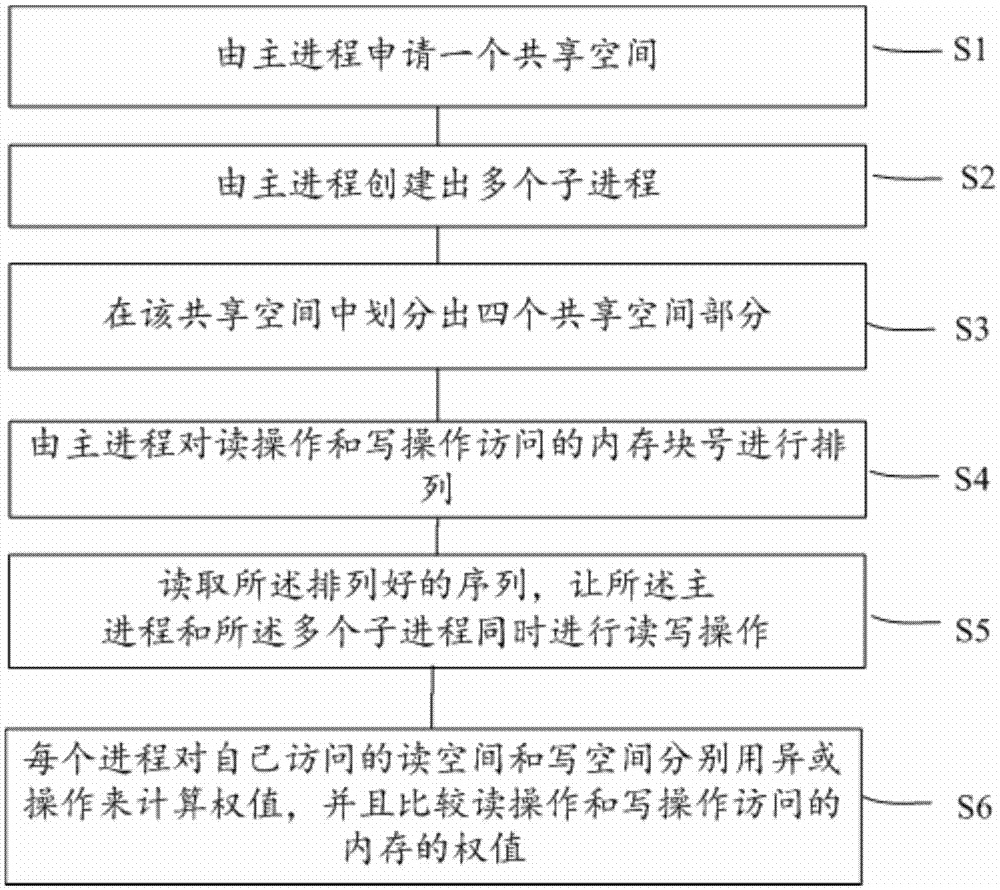

[0022] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0023] The basic idea of the present invention is to allow multiple processes to concurrently perform read and write access to non-repeated memory addresses, and then check whether the access results are correct, thereby judging whether there is a problem with cache consistency. However, when the memory space is large, there are many memory address combinations for concurrent memory access. Therefore, the present invention selects the mode that is most likely to cause cache consistency problems for traversal, that is, multiple processes concurrent read and write accesses may be mapped to the same cache segment memory address.

[0024] figure 1 A flow chart of a cache consistency testing method according to a preferred embodiment of the presen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com