A positioning method for packaging and picking up chips

A positioning method and chip technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve problems such as picking up errors, and achieve the effect of avoiding picking up wrong chips and making the operation simple

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

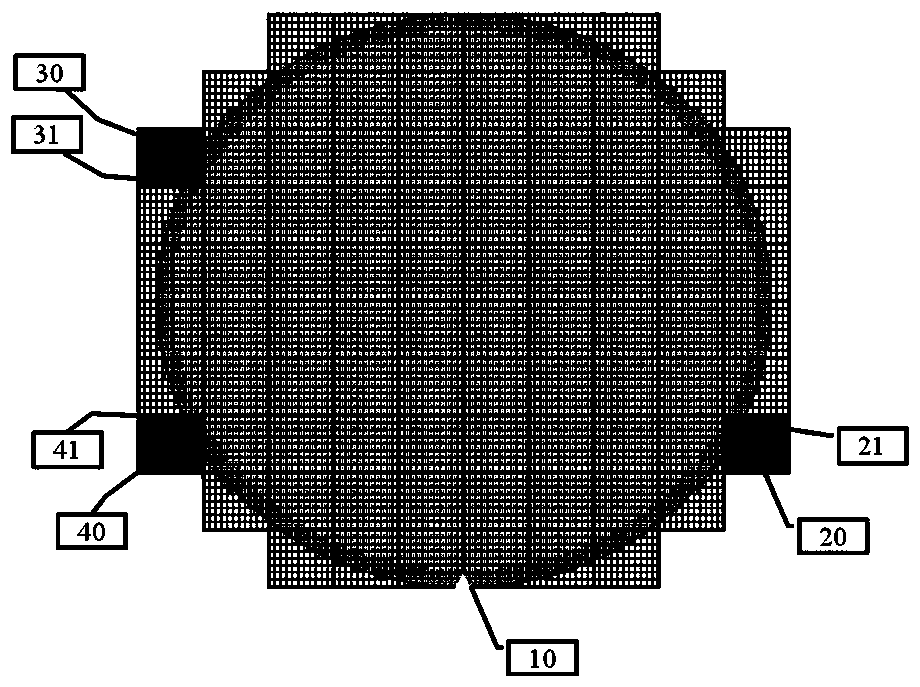

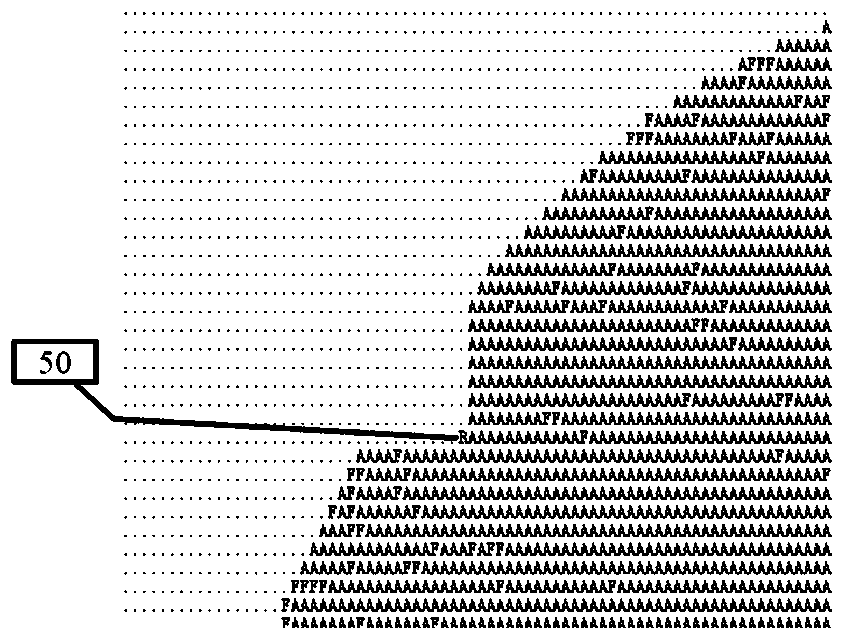

[0014] see figure 1 and figure 2 , the positioning method of the package pick-up chip of the present invention includes the modification of two parts, figure 1 Arrangement for the exposure area of the actual wafer and its integrated circuit, where 10 is the positioning notch (Notch) of the wafer, and areas 20, 30, and 40 are the least exposed areas of effective chips on the edge; figure 2 It is a part of the wafer map (Wafer Map) of the wafer test, and the positioning point 50 is the chip position of the wafer map corresponding to the physical positioning area.

[0015] see figure 1 and figure 2 , T2174 and other series of products based on the positioning method of the present invention have been mass-produced, and there are no errors in wafer manufacturing, wafer testing, and packaging and pick-up stages.

[0016] Adopt the positioning method of the integrated circuit production, testing and packaging of various embodiments of the present invention to pick up the ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com