Safe chip power-down testing equipment

A security chip, electrical testing technology, applied in measuring devices, measuring electrical variables, instruments, etc., can solve the problem of inability to effectively test the power failure of the SPI interface security chip, and achieve comprehensive testing, short delay time, and flexible use.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, but it should be understood that the protection scope of the present invention is not limited by the specific embodiments.

[0019] In order to solve the problem in the prior art that the SPI interface security chip cannot be effectively tested for power-down, the present invention proposes a security chip power-down test device.

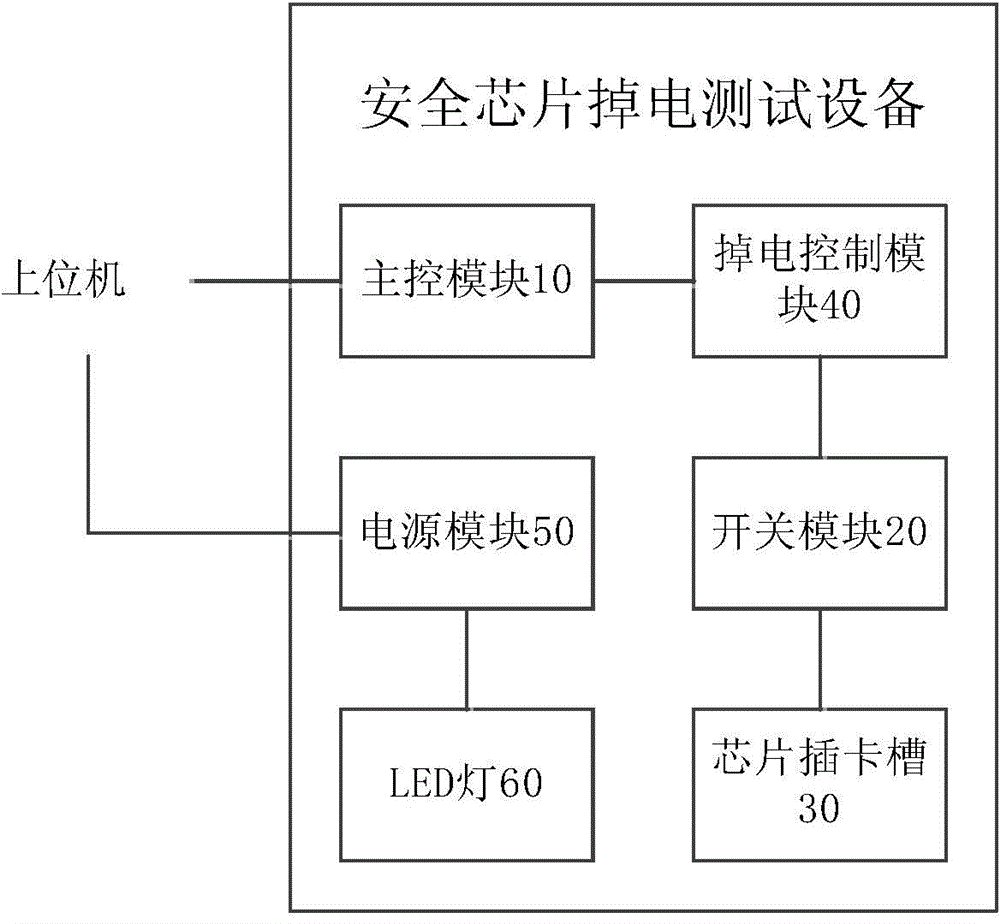

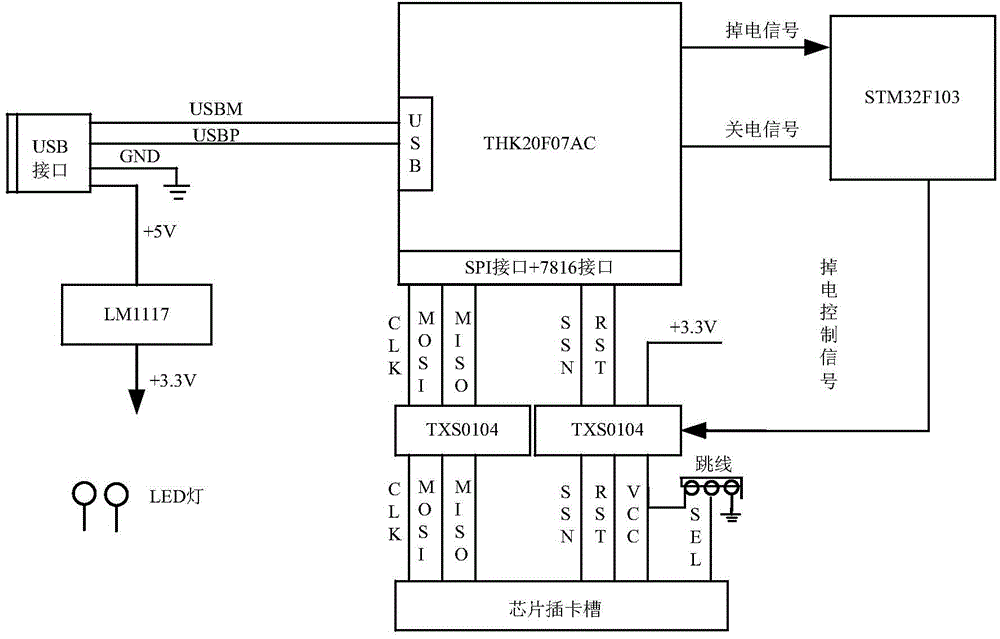

[0020] Such as figure 1 As shown, the safety chip power-down testing device of the present invention mainly includes: a main control module 10, a switch module 20, and a chip card slot 30. Since the main control module 10 itself has limited pins, the present invention may also include a power-down control module 40 . The main control module 10 is provided with a USB interface, an SPI interface, and a 7816 interface. The main control module 10 communicates with the host computer through the USB interface, receives...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com