A dll output circuit and a method for ensuring that dram power-saving mode exits normally

A power-saving mode and output circuit technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of unstable internal power supply system of DRAM and inability to compensate for voltage disturbance, and achieve the effect of reducing logic errors and quality loss.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

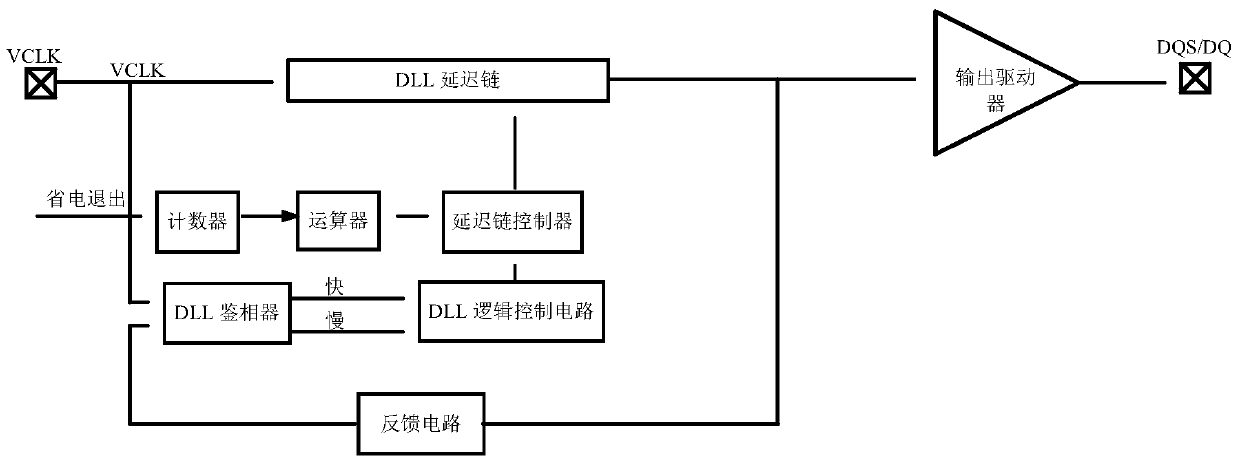

[0024] When the DRAM exits the power-saving mode, it automatically adjusts the number of DLL delay units inside the DLL (delay phase-locked loop) to compensate for the transient voltage disturbance at this time. The number of units to be adjusted and the duration of adjustment can be externally configured according to the actual working conditions of the DRAM, or automatically adjusted according to the working frequency.

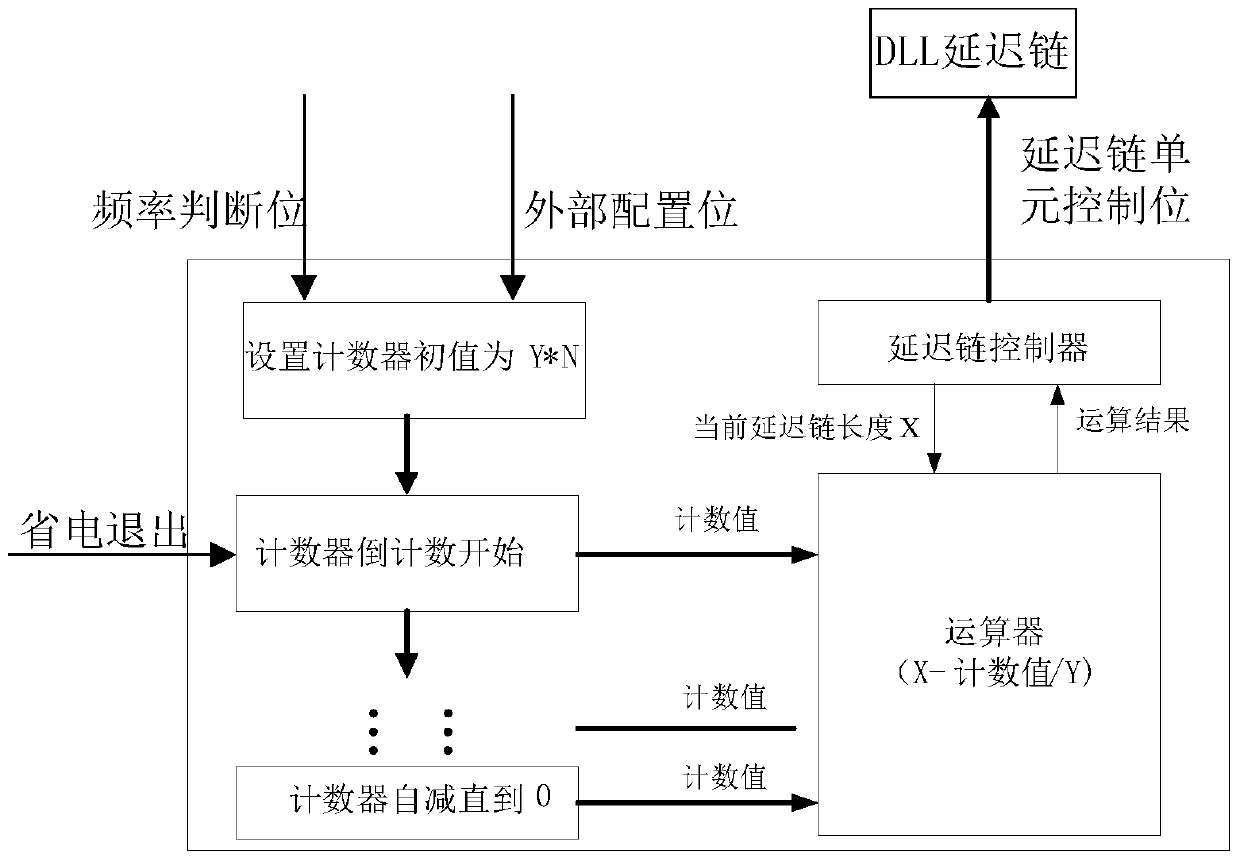

[0025] The specific process is:

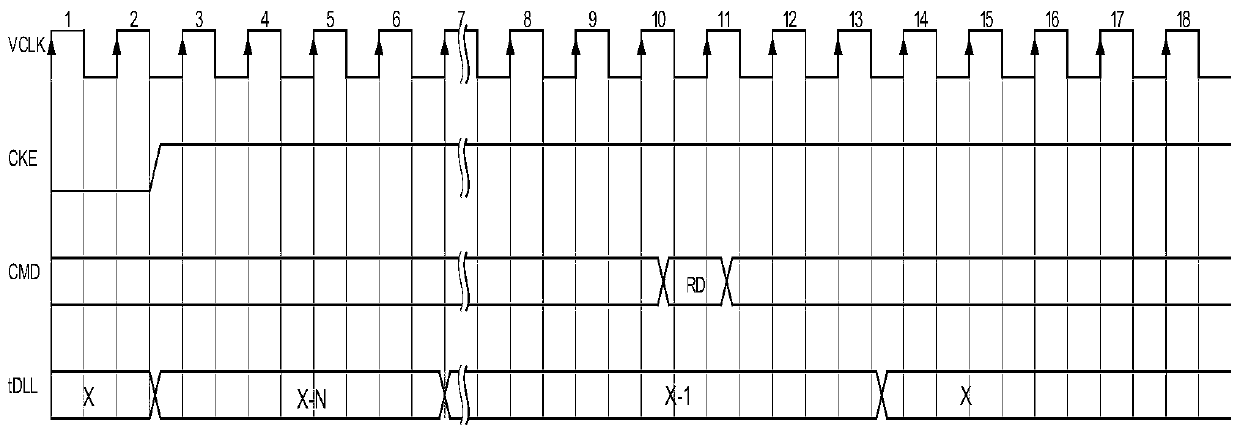

[0026] When the DRAM is in power-saving mode, the number of DLL delay units locked by the DLL delay chain is X;

[0027] After exiting the power saving mode, the number of DLL delay units locked by the DLL delay chain is quickly adjusted to X‐N

[0028] After a certain time Y, the number of DLL locking delay units is adjusted to X-(N-1) again

[0029] After the YxN time period, the number of DLL lock delay units changes back to the original X

[0030] The implemented module diagram is:

[0031] The adjusted N and Y can b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com