NEON vectorization conversion method for ARM (Advanced RISC Machine) binary code

A technology of binary code and conversion method, applied in the field of automatic parallelization of embedded virtual SIMD, can solve the problem of not reducing the overall number of instructions, increasing instructions, etc., and achieving the effect of reducing the number of visits, reducing the number of visits, and reducing the time overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

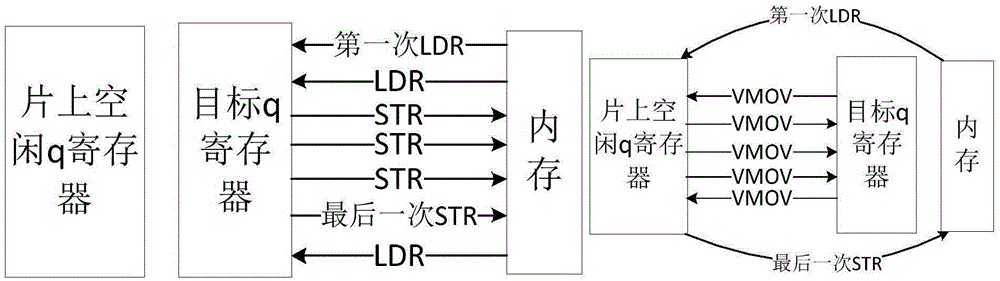

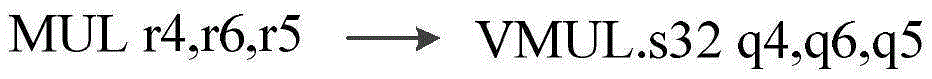

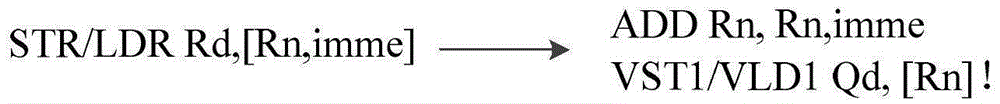

[0077] The NEON vectorization conversion method of a kind of ARM binary code of the present invention, its core is:

[0078] 1. In the target-optimized ARM program, some memory access instructions have non-linear address increment or decrement memory access, non-equal length increment or decrement memory access, and memory access exceeding the step limit of the NOEN memory access instruction due to its memory access mode. It cannot be translated into NEON instructions due to reasons such as storage and conditionally executed memory access (that is, conditional memory access instructions). Before the present invention translates ARM instructions into NEON instructions, it first analyzes the instructions that constitute the loop and the instructions that need to be translated in groups, strips them to reduce the burden of subsequent memory access pattern analysis, and then optimizes all memory access in the target program Instructions are counted, and the similarities and differ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com