A synchronous clock system for multiple high-speed signals of a super-large area array cmos camera

A technology of synchronous clock and high-speed signal, applied in the direction of automatic power control, electrical components, etc., can solve the problem of unable to reduce jitter, unable to control the duty cycle, etc., to solve the design layout and wiring, difficult to change the duty cycle, reduce The effect of small transmission distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

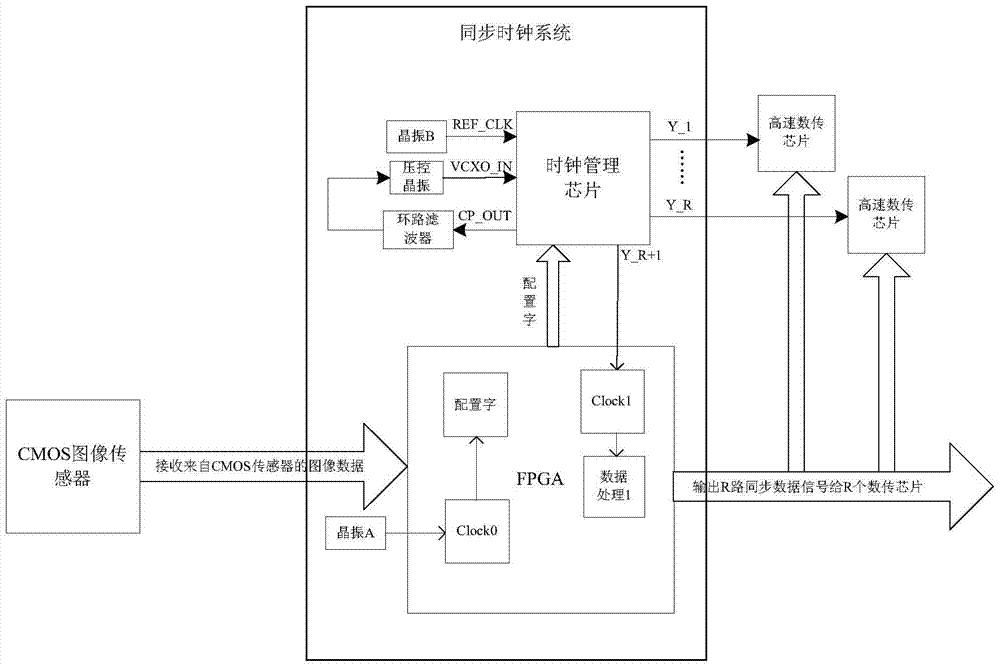

[0025] According to the characteristics of super large area array CMOS camera image transmission, and output multiple high-speed signals at the same time, the present invention designs a working crystal oscillator A, a reference crystal oscillator B, T voltage-controlled crystal oscillators, a programmable logic device FPGA, and T phase-locked loops Functional clock management chip, T loop filter clock system, the specific structure is as follows figure 1 shown. The system uses T clock management chips, voltage-controlled crystal oscillators, loop filters, and a reference crystal oscillator B to form T phase-locked loop structures, which can simultaneously output T*R synchronous clocks with the same phase, where T≥ 2. R≥2, T and R are both positive integers, and R is the number of synchronous clock channels that each clock management chip can output to subsequent R high-speed data transmission chips.

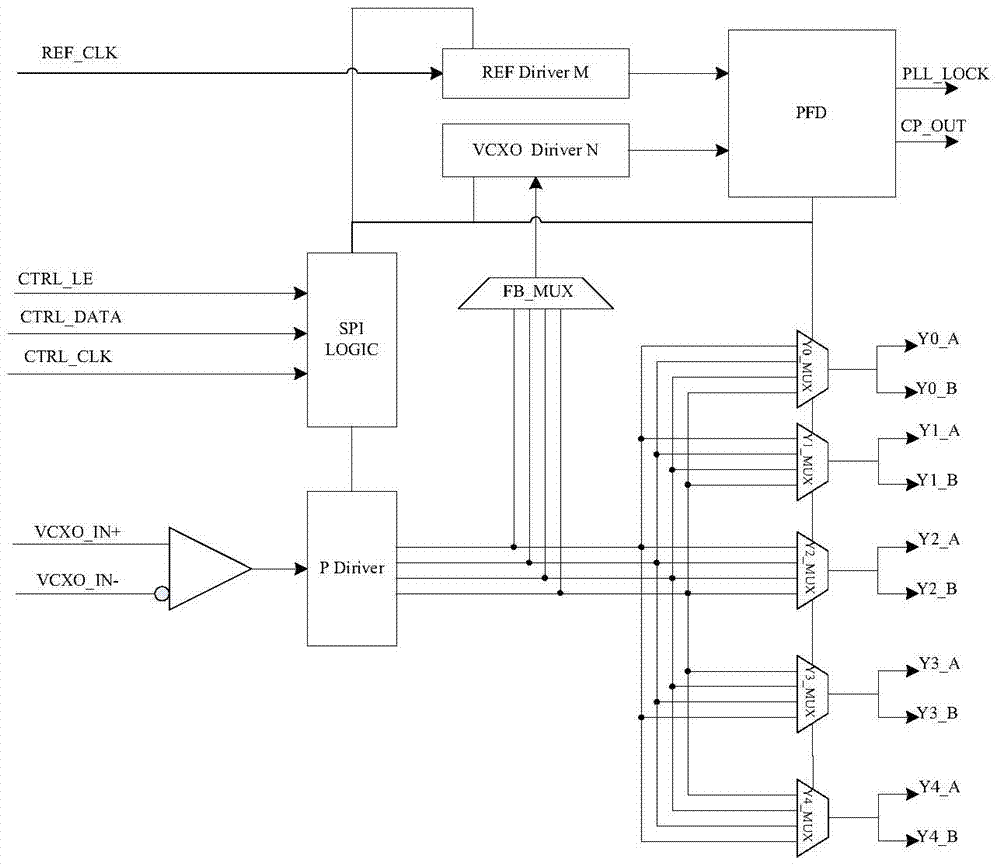

[0026] The clock management chip generally needs to be configured by the F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com