DC deviation correcting method and device

A technology of DC offset and correction method, which is applied in the field of radio frequency communication, can solve the problems of narrow application range, lower dynamic range of amplifier and ADC, and lack of real-time performance, so as to achieve good real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

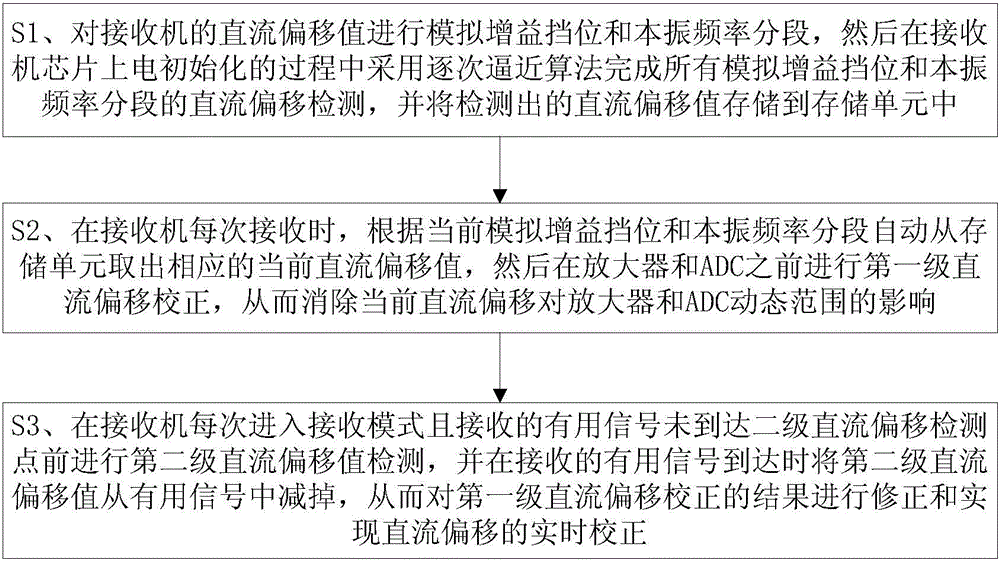

Method used

Image

Examples

no. 1 example

[0112] The present invention adopts a two-stage DC offset correction method and device: the first stage corrects the DC offset before the amplifier and ADC, avoiding the problem of non-linear distortion caused by saturation of the amplifier or ADC due to excessive DC; the second stage The second stage corrects the DC offset in real time after the amplifier and ADC on the basis of the first stage DC offset correction, which solves the problem of real-time DC changes caused by changes in the environment and temperature. In consideration of balancing precision, area, and power consumption, the successive approximation algorithm in this embodiment adopts a five-bit successive approximation algorithm, and the DAC adopts a five-bit DAC.

[0113] Concrete implementation process of the present invention is as follows:

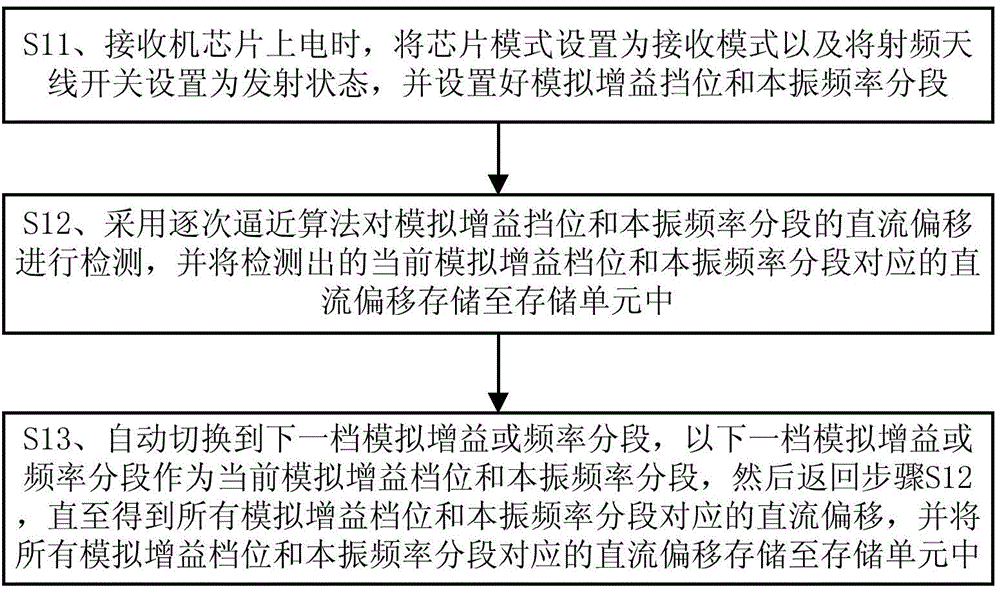

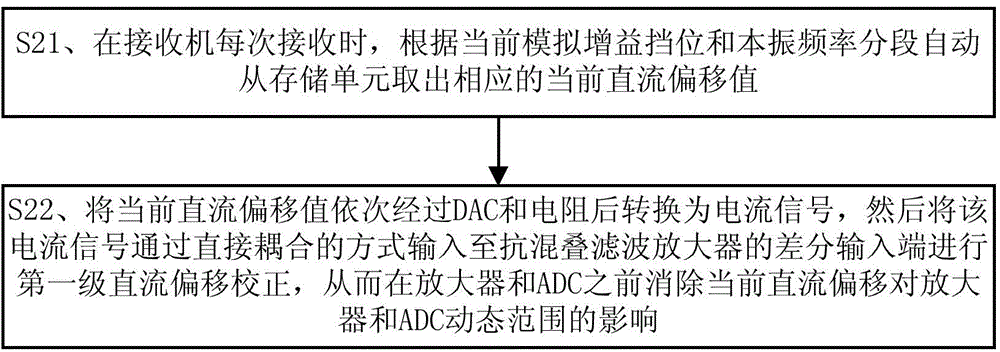

[0114] (one). First-level DC offset correction method and device

[0115] The first level of DC offset correction is only done once when the receiver chip is powered...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com