Multi-core processor directory cache replacement method

A multi-core processor and cache replacement technology, applied in the fields of electrical digital data processing, instruments, memory systems, etc., can solve problems such as damage to the overall performance of multi-core processors, waste of DirectoryCache capacity, and DirectoryCache capacity conflicts.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be further described in conjunction with the accompanying drawings.

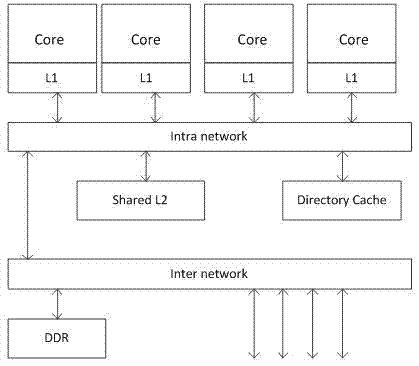

[0045] combine figure 1 , a multi-core processor directory cache replacement system includes a two-level cache structure, composed of four Tile, each Tile includes a processor core and an L1Cache, connected to the L2Cache and directory cache through an interconnection network, shared by all processor cores L2Cache, the processor is connected to DDR and other processors through an external network;

[0046] The interactive messages between L1Cache and directory cache determine the number of no-message replacements that occur in a certain cache group of L1Cache corresponding to each processor core;

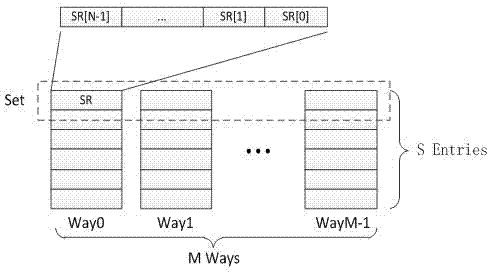

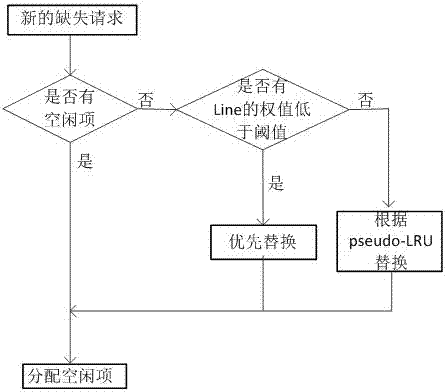

[0047] The directory cache adds a no-message replacement count vector group for each L1Cache cache group to save the number of no-message replacements that occur in each L1Cache in the cache group; when the directory cache is replaced, according to the current replacement policy ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com