Method for manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as large chipped corners, affecting the electrical performance of semiconductor devices, and sharp tops of shallow trench isolation structures, etc., to achieve improved Smoothness, improve the performance of semiconductor devices, prevent the effect of uneven electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

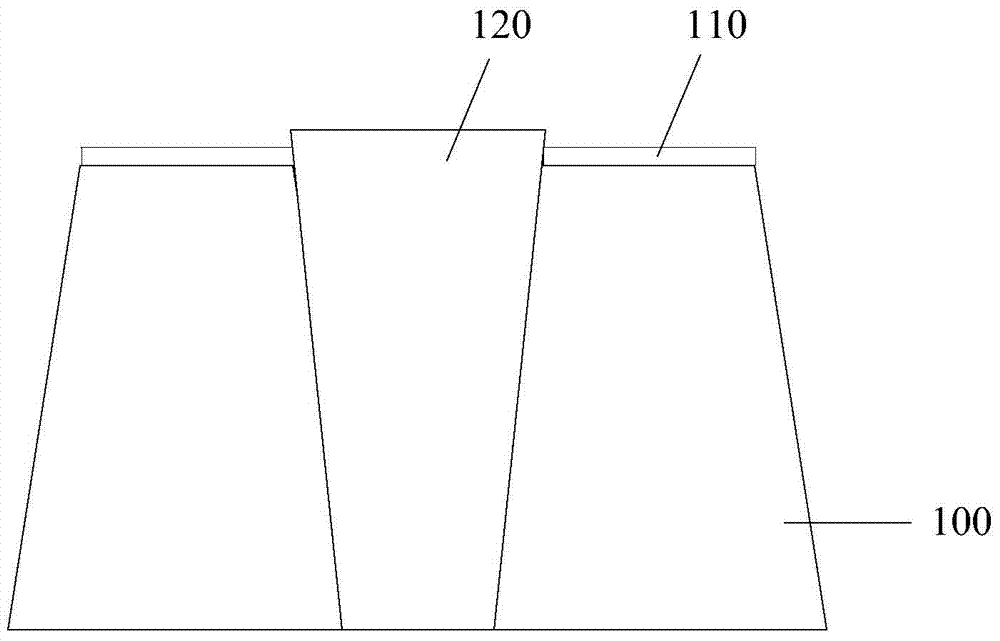

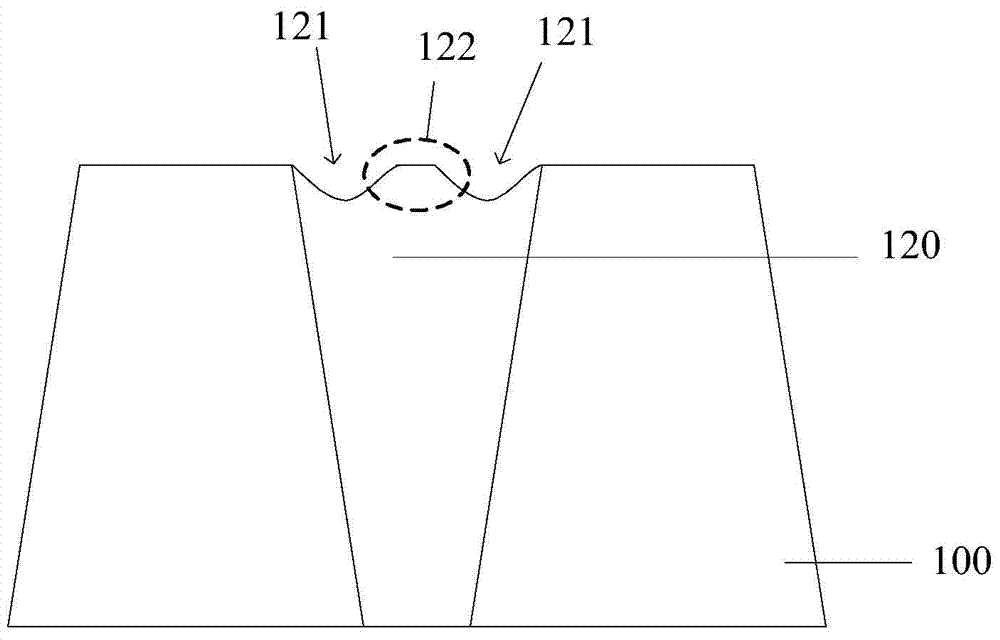

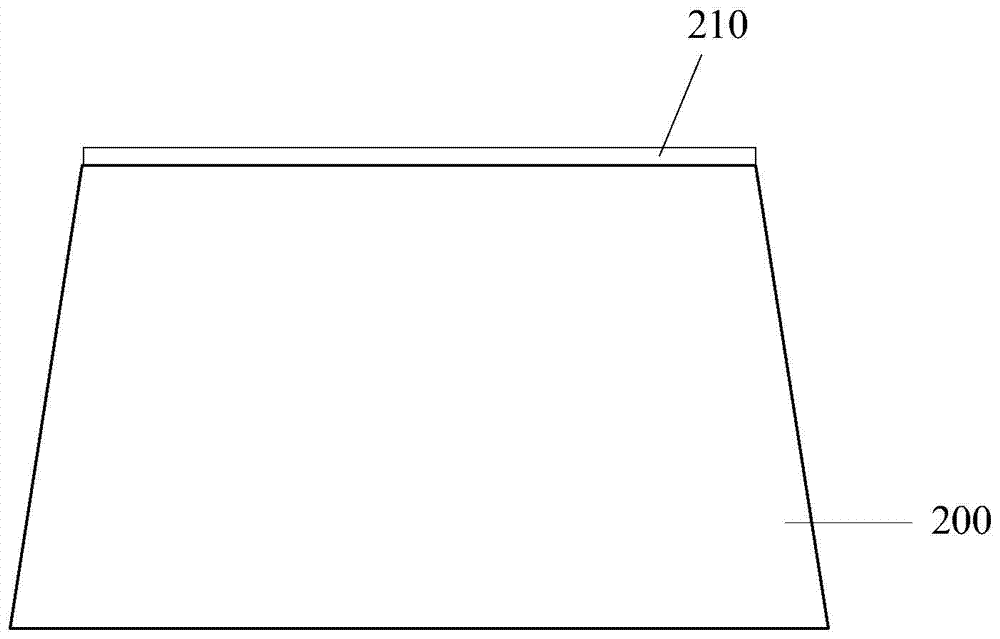

[0034] As mentioned in the background technology, the existing semiconductor device manufacturing method uses a wet etching process to remove the pad oxide layer on the semiconductor substrate. The wet etching process will not only etch the pad oxide layer, but also the shallow trench The insulating material of the isolation structure is etched, because the top side edge of the shallow trench isolation structure is easily wetted by the wet etching solution, so the top side edge of the shallow trench isolation structure is easy to be etched into a large missing corner. And because the wet etching process is an isotropic etching process, the width of the larger notch is usually twice the depth, that is, the width of the notch is larger, resulting in a gap between the top and middle of the shallow trench isolation structure. Form sharp cusps. The sharp protrusions will lead to uneven surface of each layer structure subsequently formed on the shallow trench isolation structure, re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com