A dual-output dc‑dc oscillator circuit

A DC-DC, oscillator technology, applied in the field of DC-DC oscillator circuit, can solve the problems of mutual interference, large RMS current, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

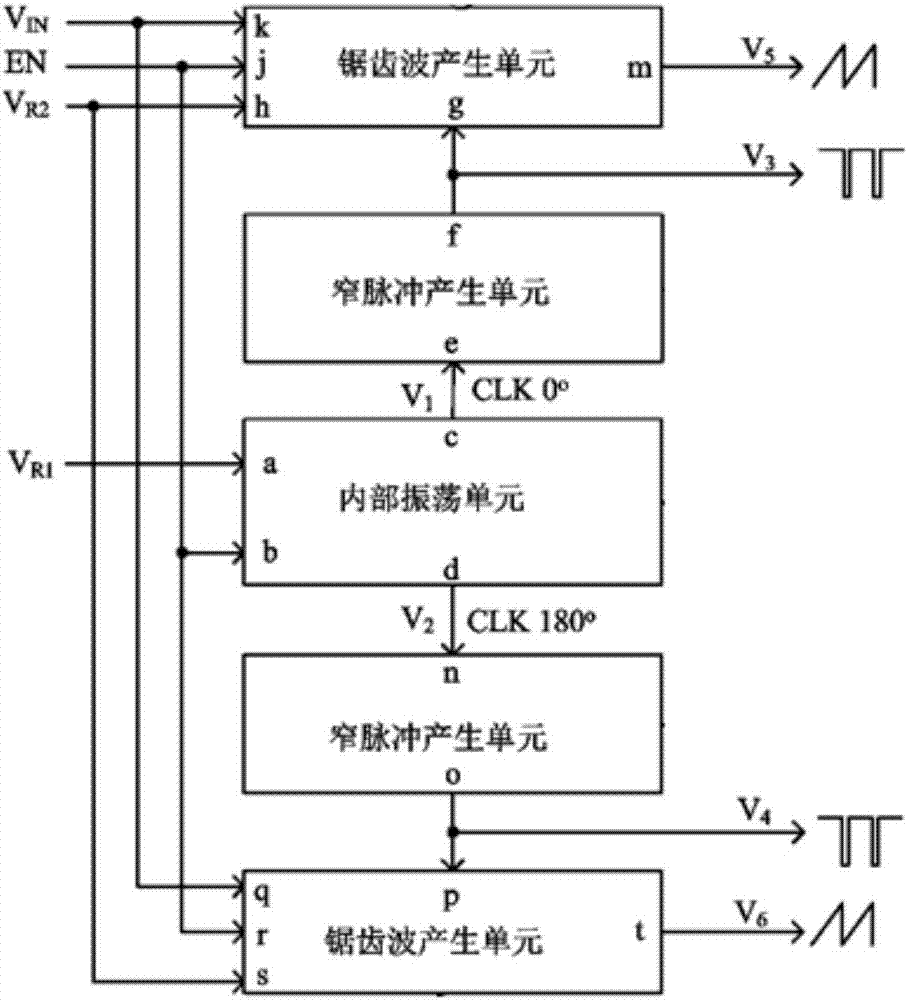

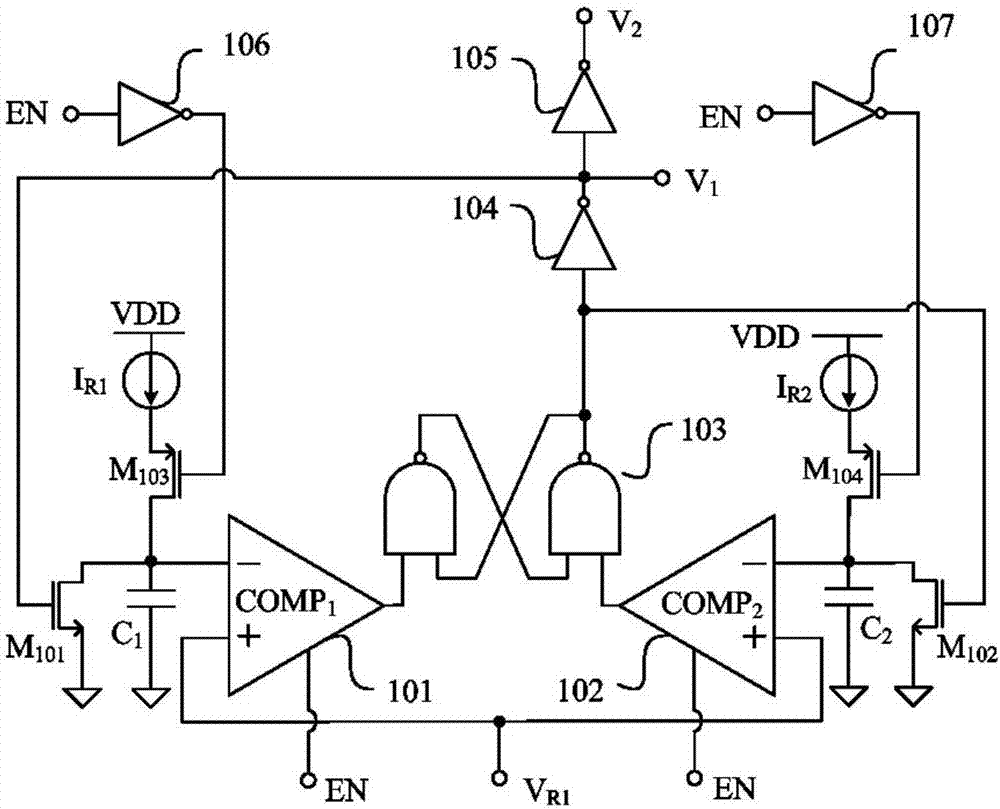

[0055] See figure 1 The present invention includes an internal oscillation unit capable of generating a constant clock signal, a first narrow pulse generating unit and a second narrow pulse generating unit capable of converting the internal clock signal into a narrow pulse signal with a fixed pulse width, and two phase differences 180 A first sawtooth wave generating unit and a second sawtooth wave generating unit of a high-degree sawtooth wave signal;

[0056] The internal oscillation unit is respectively connected to the first narrow pulse generating unit and the second narrow pulse generating unit, and the internal oscillation unit is connected to the reference voltage V R1 And the enable signal EN, the phase difference between the constant clock signal output by the internal oscillation unit to the first narrow pulse generating unit and the constant clock signal output to the second narrow pulse generating unit is 180 degrees, the first narrow pulse generating unit and The ou...

Embodiment 2

[0093] The internal oscillation unit and the narrow pulse generation unit of this embodiment are the same as those in the first embodiment, and the circuit of the tooth wave generation unit is changed.

[0094] See Figure 5 , The first sawtooth wave generating unit and the second sawtooth wave generating unit have the same circuit structure, and both include an error amplifier 301, a second D flip-flop 302, a ninth inverter 303, and an NMOS tube M 301 , NMOS tube M 303 , NMOS tube M 305 , NMOS tube M 307 , PMOS tube M 302 , PMOS tube M 304 , PMOS tube M 306 , PMOS tube M 308 , The third capacitor C 3 , The fourth capacitor C 4 And current source I R3 ;

[0095] The non-inverting input terminal of the error amplifier 301 is connected to the reference voltage V R2 , The inverting input terminal is connected to its output terminal, and the NMOS tube M is connected at the same time 301 , NMOS tube M 305 And PMOS tube M 302 , PMOS tube M 306 The source of the error amplifier 301 is conne...

Embodiment 3

[0102] The internal oscillation unit and the sawtooth wave generating unit of this embodiment are the same as those in the first embodiment, and the circuit of the narrow pulse generating unit is changed.

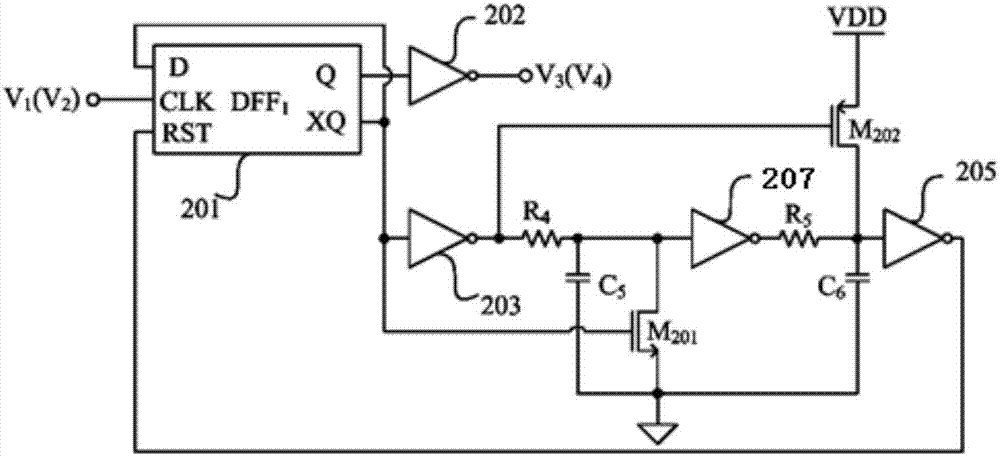

[0103] See Image 6 , The first narrow pulse generating unit and the second narrow pulse generating unit have the same circuit structure, and both include a first D flip-flop 201, a fifth inverter 202, a sixth inverter 203, a NAND gate 204, and an eighth inverter. Phaser 205, tenth inverter 206, seventh capacitor C 7 ;

[0104] The clock input terminal CLK of the first D flip-flop 201 is connected to V 1 Or V 2 , Its input terminal D is connected to the input terminal of the tenth inverter 206 and one of its output terminals XQ is connected at the same time, the output terminal XQ of the first D flip-flop 201 is connected to the input terminal of the sixth inverter 203, and the reset terminal RST is connected to The output terminal of the eighth inverter 205, and the other outpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com