Image sensor parasitism insensitiveness simulation accumulator and time sequence control method

An image sensor and accumulator technology, which is applied in image communication, TV, color TV components and other directions, can solve problems such as reducing the accumulation effect, and achieve the effect of no increase in power consumption, a simple structure, and an increase in the number of effective accumulation stages.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The invention improves the analog accumulator used in the TDI CIS, and reduces the limitation of parasitic in the circuit to the number of accumulation stages by adding a decoupling switch. It can greatly increase the number of effective accumulation stages of the accumulator without increasing the area and power consumption of the circuit.

[0021] The technical scheme adopted in the present invention is:

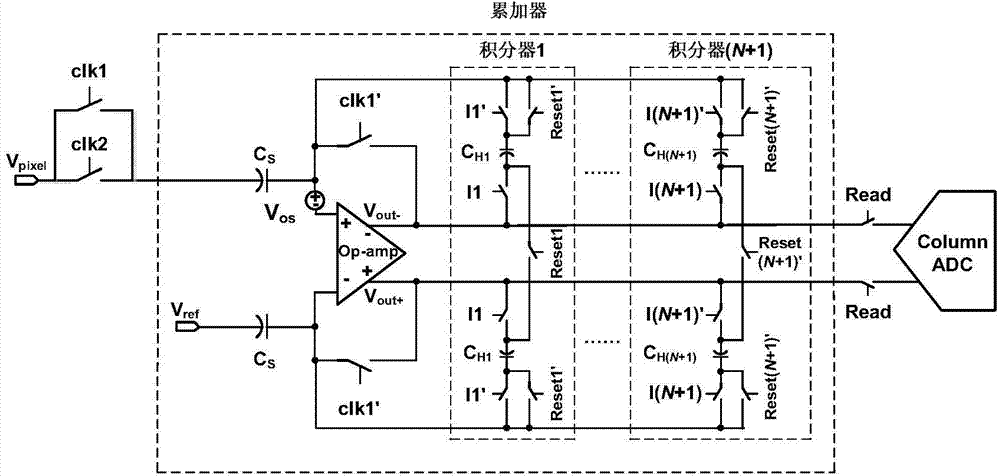

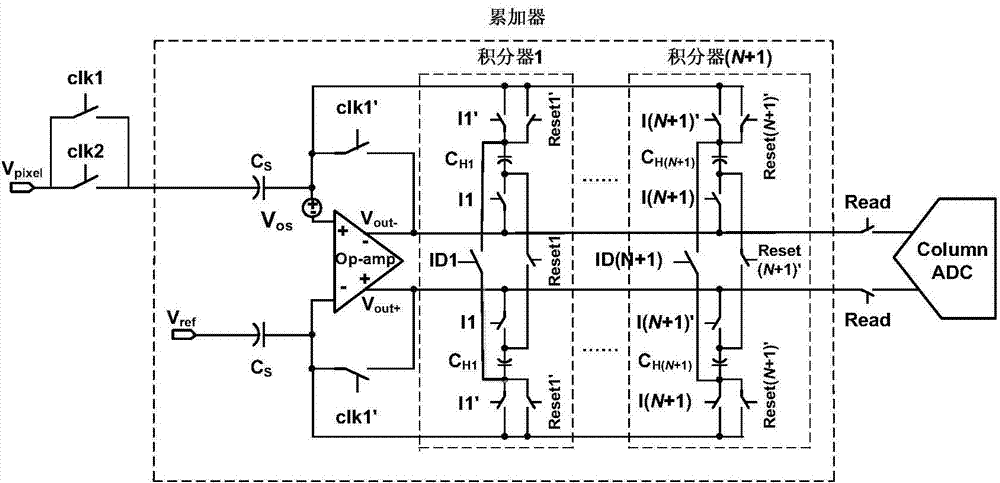

[0022] image 3 It is the structural diagram of the analog accumulator proposed by the present invention. In order to realize the elimination of parasitic, it adds a decoupling switch ID in each stage integrator on the basis of the existing accumulator, and connects the two integration capacitors Upper plate. The structure eliminates the parasitic in the integrator by controlling the decoupling switch, and greatly increases the effective accumulation stages of the accumulator.

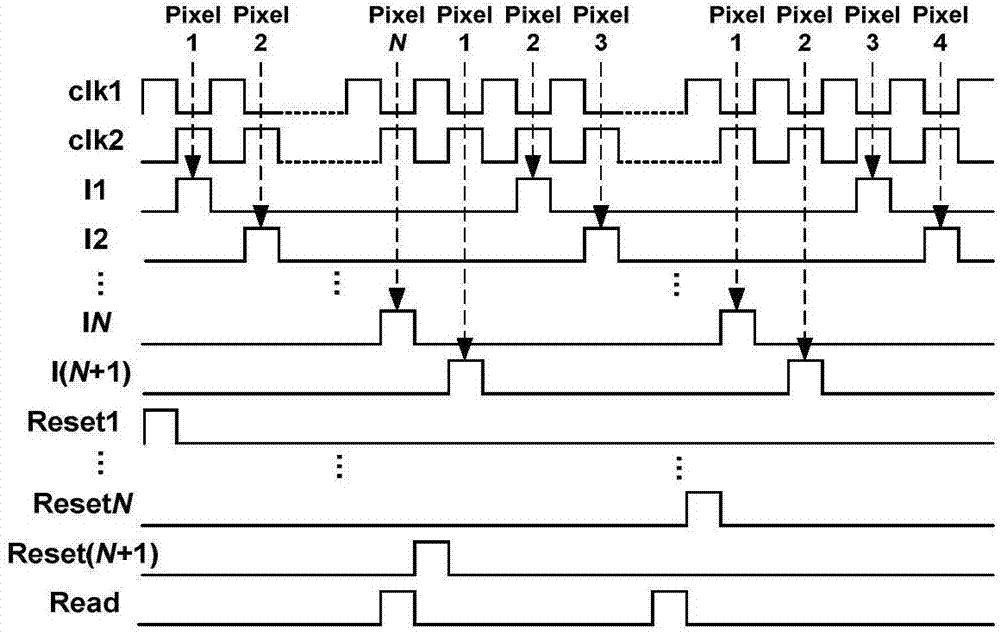

[0023] Figure 4 It is the timing diagram of the analog accumulator proposed by the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com