Method for constructing UVM verification component by utilizing existing Verilog BFM

A component and structure technology, applied in the field of computer structure verification, to save time and shorten the verification cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Below in conjunction with accompanying drawing description.

[0019] Such as figure 1 , the middle is the logical description of the circuit under test, the left is the bus model BFM generated by the stimulus, and the right is the bus model BFM for response detection. Whether it is a stimulus generation or a response detection model, it is generally packaged in a Verilog module. In the module, various stimuli are generated or various responses are collected through functions or tasks to simulate external devices of the circuit under test. The three parts are instantiated in the top level and connected to each other. A sample program is:

[0020]

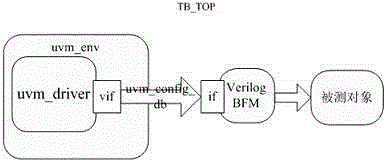

[0021] Such as figure 2 , the left side of the picture is the object under test (DUT) in the UVM verification platform. The middle part is the environment subject uvm env, which includes multiple entities uvm agent. Each uvm agent includes a sequencer, a driver, and a monitor. Each uvm agent is connected to the objec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com