Anti-breakdown soi folded gate insulated tunneling bipolar transistor and manufacturing method thereof

A bipolar transistor and gate insulation technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as increased static power consumption, increased sub-threshold swing of MOSFETs devices, and small forward conduction current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

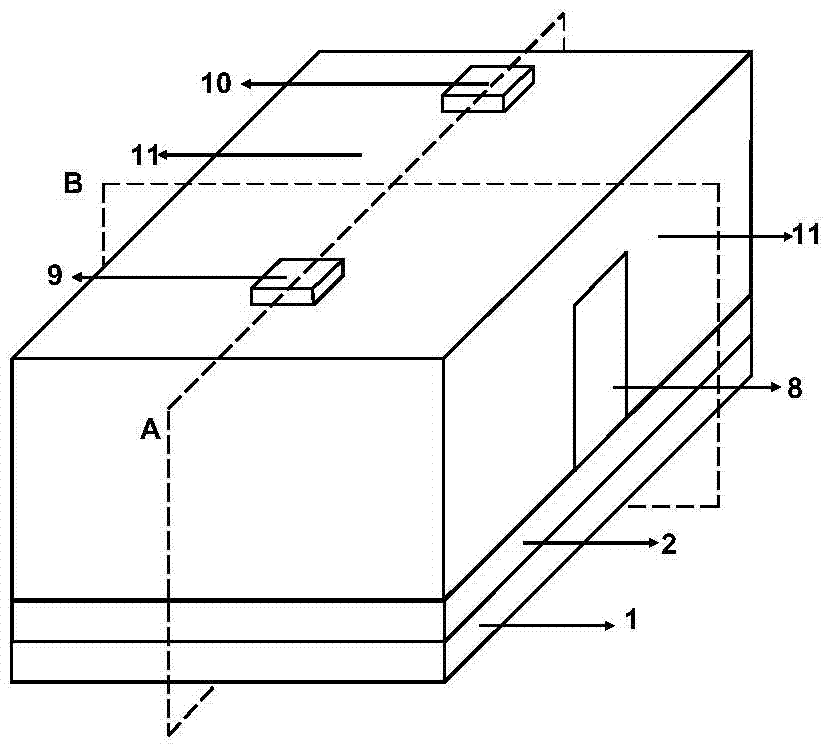

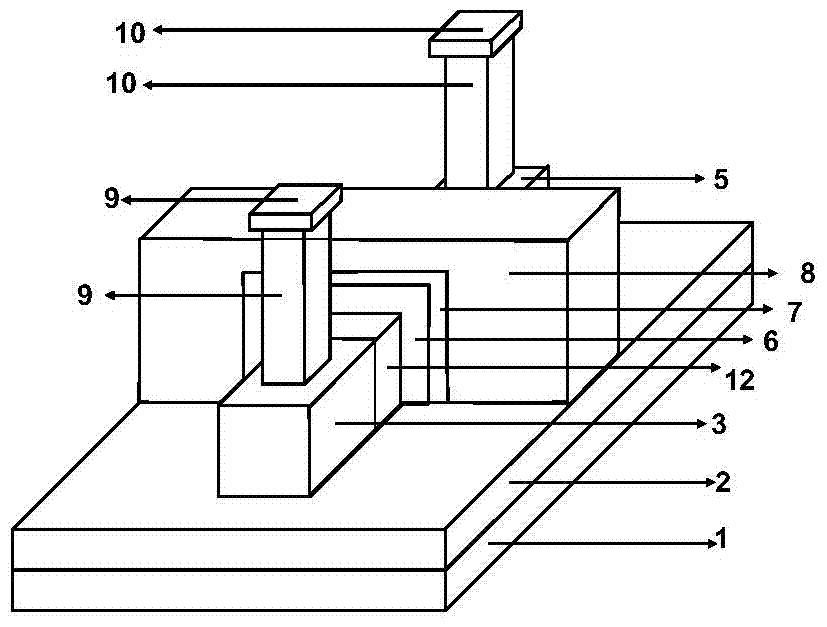

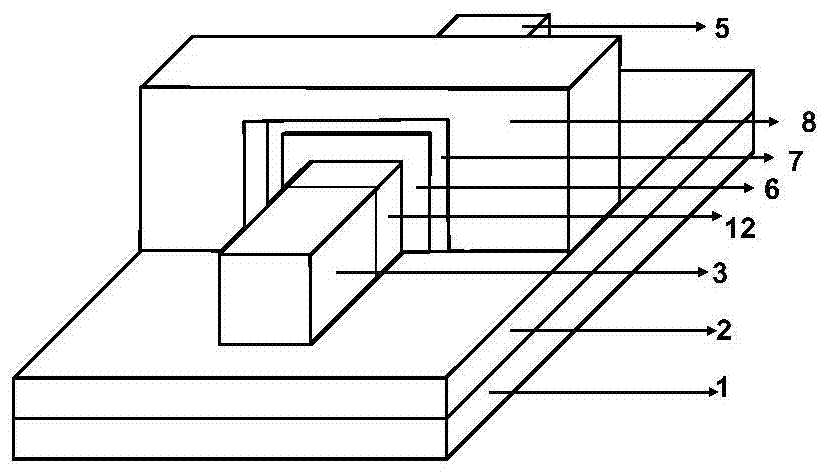

[0084] Below in conjunction with accompanying drawing, the present invention will be further described: figure 1 It is a schematic diagram of a three-dimensional structure of an anti-breakdown SOI folded gate insulated tunneling bipolar transistor formed on an SOI substrate in the present invention; figure 2 A schematic diagram of a three-dimensional structure after peeling off the blocking insulating layer 11 for the anti-breakdown SOI folded gate insulated tunneling bipolar transistor of the present invention; image 3 A schematic diagram of a three-dimensional structure after peeling off the emitter 9, the collector 10 and the blocking insulating layer 11 for the anti-breakdown SOI folded gate insulated tunneling bipolar transistor of the present invention; Figure 4 A schematic diagram of a three-dimensional structure after peeling off the emitter 9, the collector 10, the blocking insulating layer 11 and the folded gate electrode 8 for the anti-breakdown SOI folded gate i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com