High-resistance silicon substrate based LDMOS MMIC chip

A high-resistance silicon and chip technology, applied in the field of LDMOS MMIC chips, can solve the problems of reducing LDMOS MMIC performance, reducing inductance Q and self-resonant frequency, increasing parasitic capacitance to ground, etc., to increase bandwidth and power conversion efficiency, and reduce PN junction capacitance, increasing the effect of isolation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

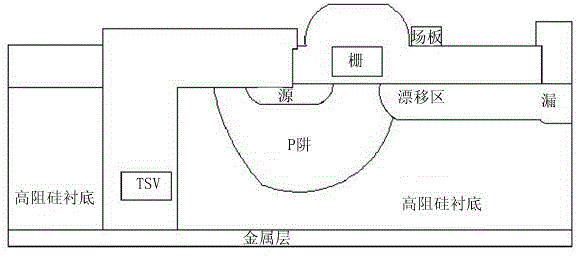

[0009] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

[0010] In LDMOS devices, there is a large current between the source and the ground on the back of the chip. In order to reduce the resistance between the source and the ground, a low-resistance heavily doped P-type silicon substrate is used, and a low-resistance P-type silicon layer is epitaxially grown on it, and LDMOS devices are fabricated in the low-resistance epitaxial layer. The source of LDMOS The pole is connected to the heavily doped P-type substrate through a heavily doped P region.

[0011] LDMOS-based MMIC (Monolithic Microwave Integrated Circuit) needs to integrate passive components such as inductors in the chip. However, the isolation between the low-resistance and heavily dope...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com