Device backboard high-speed bus link layer communication protocol based on M-LVDS

A high-speed bus and communication protocol technology, applied in the bus network, data exchange through path configuration, electrical components, etc., can solve problems such as mismatching bus design requirements, low stability and reliability, and bus failure , to achieve the effect of improving signal integrity, improving system stability, and meeting high real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be further described in detail below with reference to the drawings and specific embodiments.

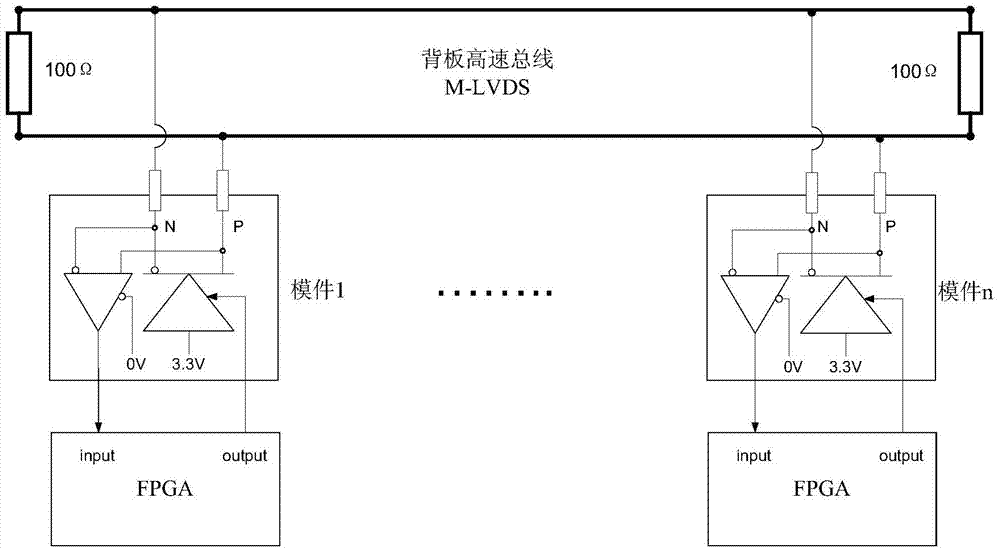

[0035] Such as figure 1 As shown, an M-LVDS-based device backplane high-speed bus link layer communication protocol. The M-LVDS-based device backplane high-speed bus uses differential signals from an interface chip that supports M-LVDS level standards to build a bus peripheral hardware loop. Interface chip (attached figure 1 The single-ended input and separate output of several modules in the) are connected to FPGA, and the bus link layer communication protocol control is realized by FPGA.

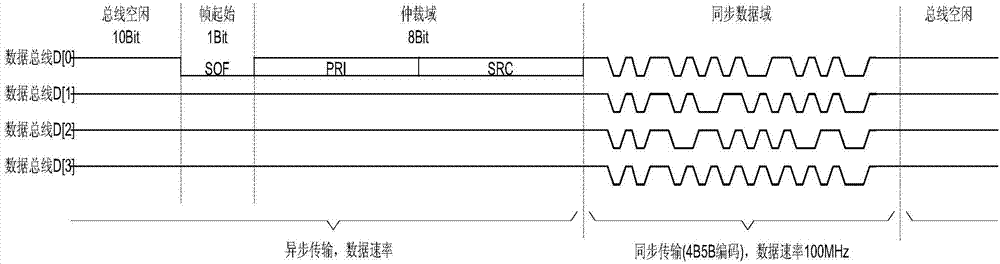

[0036] The high-speed bus on the backplane of the device adopts variable data bit width control to realize communication bandwidth configuration; it can be configured as 1-wire, 2-wire, 4-wire, 8-wire mode, which can realize 80Mbps, 160Mbps, 320Mbps, 640Mbps communication bandwidth respectively , It can also be configured with a bit width of 16-line and 32-line to ac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com