Flash memory unit and formation method thereof

A technology of flash memory storage and floating gate, which is applied in the direction of electrical components, transistors, electric solid-state devices, etc., and can solve the problems of high difficulty in size reduction and large size of flash memory storage cells, so as to reduce overlapping area, area reduction, and size reduction Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] As mentioned in the background, the size of the existing flash storage unit is relatively large, and it is difficult to further reduce the size.

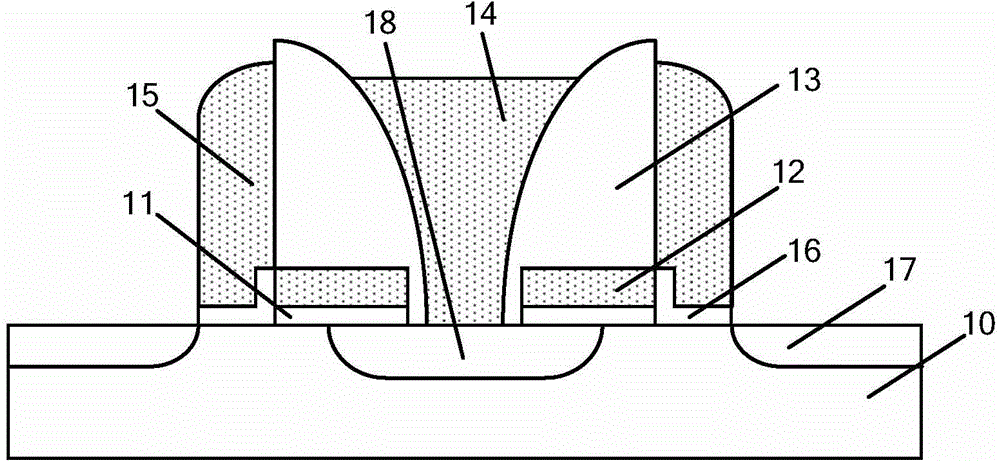

[0024] After research, please refer to figure 1 , when the flash memory cell is working, a channel region is formed between the source line doped region 18 and the bit line doped region 17, and the floating gate 12 is biased through the source line doped region 18, which can Carriers are controlled to migrate between the channel region and the floating gate 12 through the tunnel oxide layer 11 . However, if figure 1 In the shown flash storage unit, in order to apply a bias voltage to the floating gate 12, it is necessary to have an overlapping region between the source line doped region 18 and the floating gate 12, and the source line doped region 18 An applied bias voltage can be coupled to the floating gate 12 such that the floating gate 12 is biased, thus controlling the tunneling of hot carriers. Moreover, the larger t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com