Device and method for analyzing failures of TSV (through silicon via) wafer level packaged MEMS (micro-electro-mechanical systems) chips

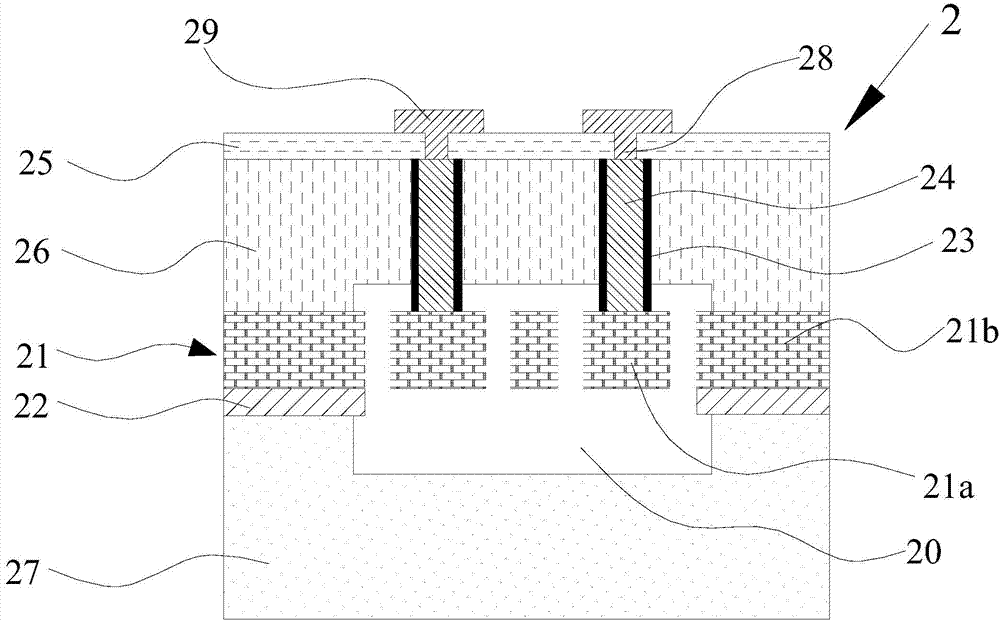

A wafer-level packaging and failure analysis technology, applied in the field of MEMS chip analysis, can solve problems such as the inability to use the response of the MEMS structure 21a by removing the cover plate, and achieve the effects of simple structure, good effect and easy operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

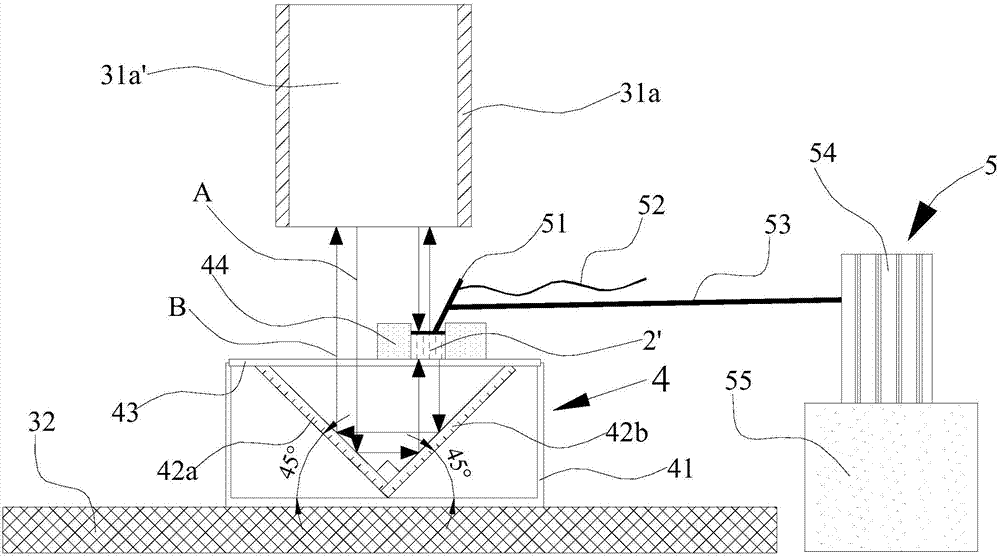

[0039] TSV wafer-level packaging MEMS chip failure analysis device such as image 3 , Figure 4 As shown, it is composed of a microscope, a reflector box 4 and a probe system 5;

[0040] The microscope comes with a light source, with a small-magnification objective lens 31a, a large-magnification objective lens 31b and a movable stage 32 for observing the MEMS structure 21a of the MEMS chip 2'to be analyzed and its movement;

[0041] The function of the reflector box 4 is to reflect light and carry the MEMS chip 2'to be analyzed. It is composed of an open top shell 41, a reflector, transparent glass 43 and a pair of positioning blocks 44 for fixing the MEMS chip 2'to be analyzed. The reflector includes Two left reflector 42a and right reflector 42b that form a 90° angle to each other. The left reflector 42a and the right reflector 42b are mounted in the housing 41 with their mirror surfaces facing upward. The left reflector 42a and the right reflector 42b are connected to the housin...

Embodiment 2

[0047] The failure analysis device of the TSV wafer-level package MEMS chip of this embodiment is different from the failure analysis device of the TSV wafer-level package MEMS chip of the first embodiment only in that the MEMS chip to be analyzed 2" is placed on the upper surface of the transparent glass 43. There is a cavity 43a at the position, such as Image 6 Shown. Since the MEMS chip 2" to be analyzed has no sealing layer 22 and cannot be directly placed on the transparent glass 43, a cavity 43a needs to be made on the transparent glass 43. In this way, when the MEMS chip 2" to be analyzed is placed, the MEMS sealing area 21b and When the transparent glass 43 is in contact, the MEMS structure 21a is located in the cavity 43a and can move freely, which solves the problem that the MEMS chip 2" cannot move after the probe 51 is stuck on the bonding block 29 in Example 1.

Embodiment 3

[0049] TSV wafer-level packaging MEMS chip failure analysis device such as Figure 7 As shown, it is composed of a microscope, a reflector box 4 and a probe system 5;

[0050] The microscope comes with a light source, an objective lens 31 and a movable stage 32 for observing the MEMS structure 21a of the MEMS chip 2" to be analyzed and its movement;

[0051] The function of the reflector box 4 is to reflect light and carry the MEMS chip 2" to be analyzed. It is composed of a shell 41 with an opening at the top, a reflector and a transparent glass 43. The reflector includes two left reflectors 42a and a right reflector at a 90° angle to each other. The mirror 42b, the left mirror 42a and the right mirror 42b are all mounted in the housing 41 with the mirror surface facing upwards. The left mirror 42a and the right mirror 42b and the bottom surface of the housing 41 have an angle of 45°, and the transparent glass 43 covers the housing. At the top opening of 41, the transparent glass ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com