Array substrate and preparing method thereof as well as capacitance embedding touch screen

A technology of array substrates and conductive wires, applied in the fields of electrical digital data processing, instruments, calculations, etc., can solve problems such as large impedance, signal delay, and impact on touch screen performance, so as to improve touch performance, avoid signal delay, and reduce production costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

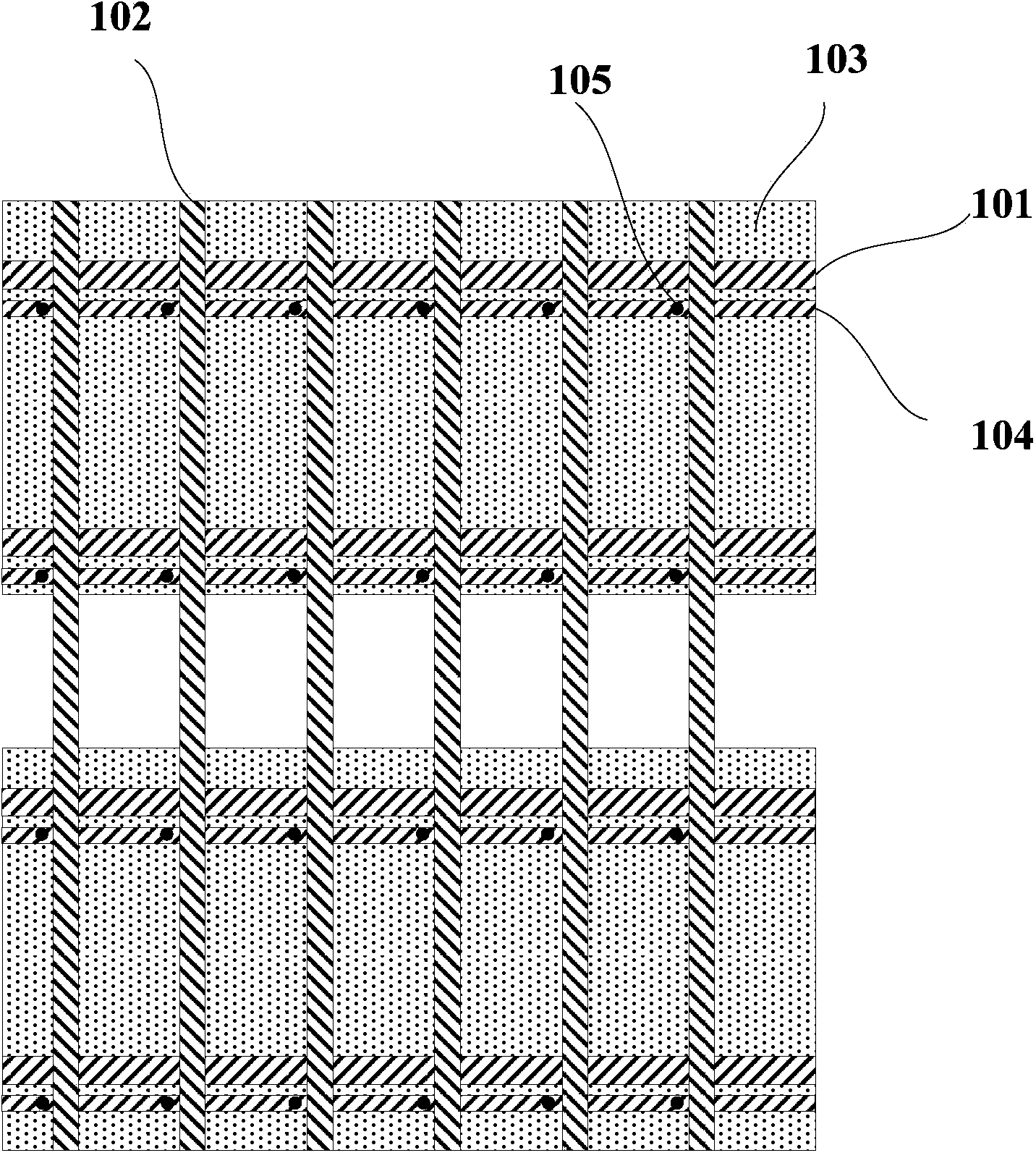

[0041] Please refer to figure 1 , figure 1 It is a schematic structural diagram of the array substrate according to Embodiment 1 of the present invention.

[0042] The array substrate comprises: a gate line layer comprising a plurality of gate lines 101 arranged in parallel, a data line layer comprising a plurality of data lines 102 arranged in parallel, and a touch driving electrode layer comprising a plurality of touch driving electrodes 103 arranged in parallel , wherein, the gate lines 101 and the data lines 102 are vertically crossed, and the touch driving electrodes 103 are parallel to the gate lines 101 .

[0043] In order to avoid the signal delay of the touch driving electrodes 103, the array substrate further includes: a first conductive line 104 provided on the same layer and with the same material as the gate line 101, the first conductive line 104 is arranged in parallel with the gate line 101, That is, it is also arranged parallel to the touch driving electrode...

Embodiment 2

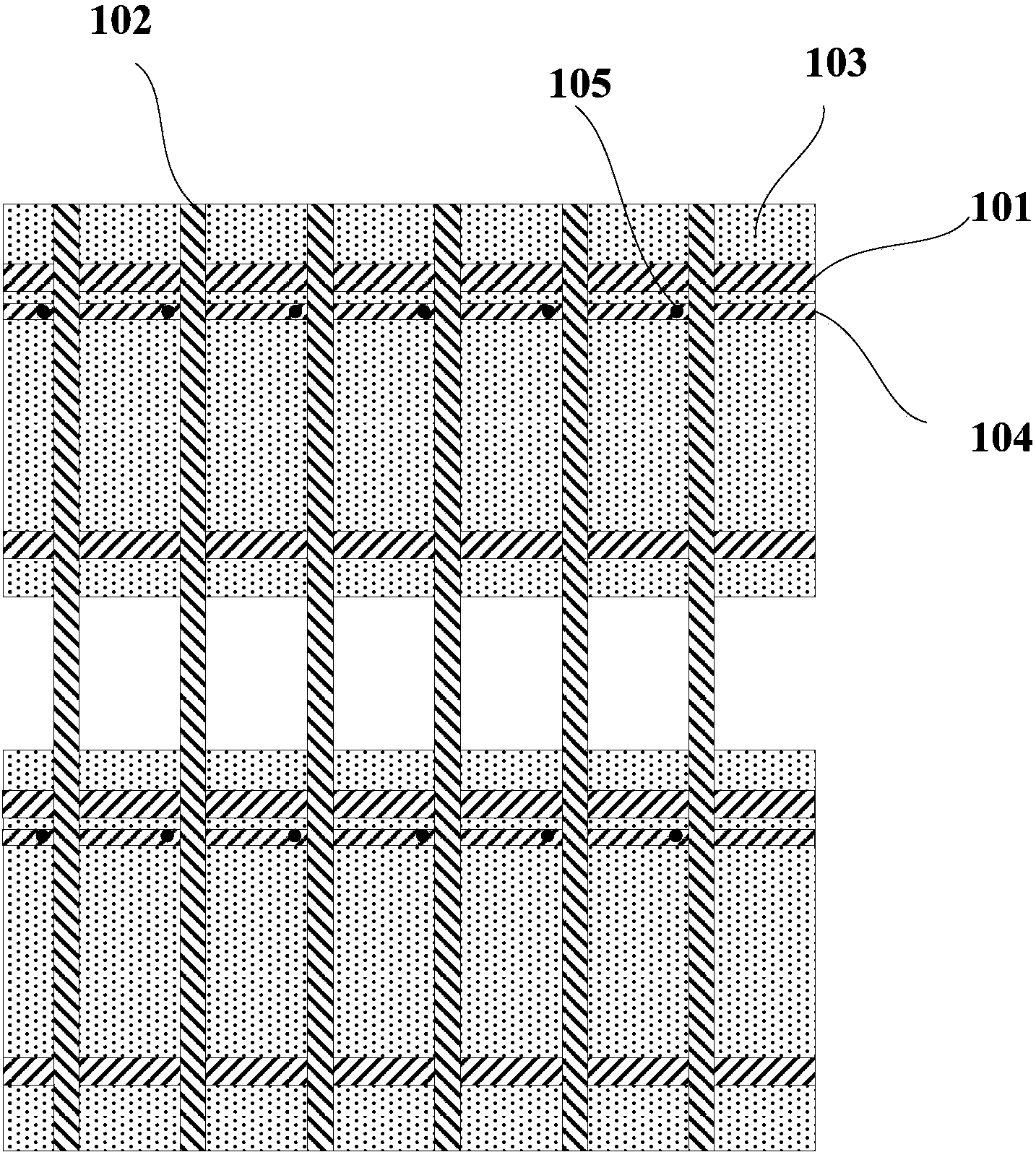

[0046] When the gate lines 101 are made of opaque metal, the first conductive lines 104 are also made of opaque metal. In order not to affect the aperture ratio of the display panel, the number of the first conductive lines 104 can be appropriately reduced. Please refer to figure 2 , figure 2 It is a schematic structural diagram of the array substrate of Embodiment 2 of the present invention. Compared with Embodiment 1, this embodiment differs in that a touch driving electrode 103 is configured with a first conductive line 104 connected in parallel thereto.

Embodiment 3

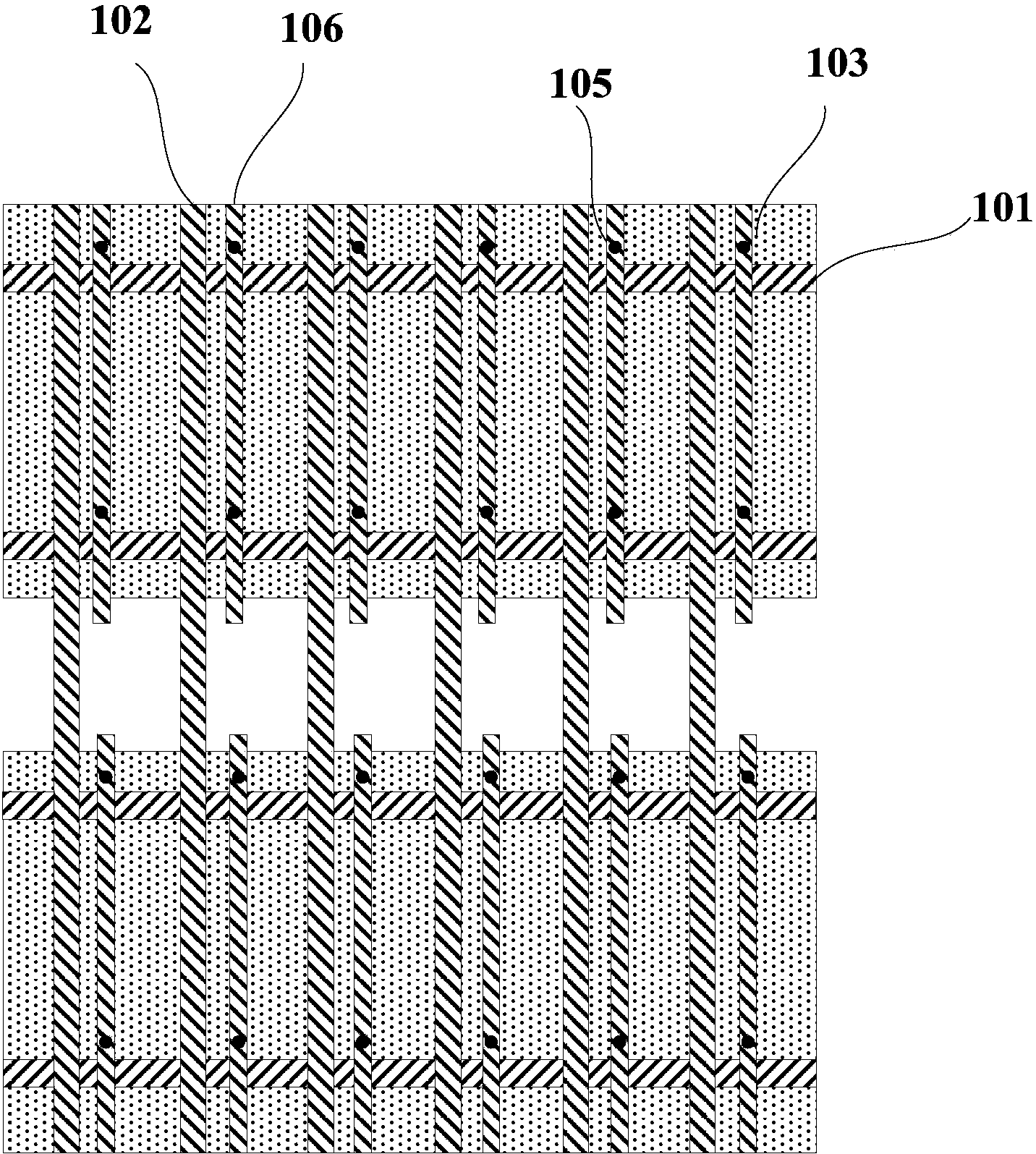

[0048] Please refer to image 3 , image 3 It is a schematic structural diagram of the array substrate according to Embodiment 3 of the present invention.

[0049] The array substrate comprises: a gate line layer comprising a plurality of gate lines 101 arranged in parallel, a data line layer comprising a plurality of data lines 102 arranged in parallel, and a touch driving electrode layer comprising a plurality of touch driving electrodes 103 arranged in parallel , wherein the gate line 101 and the data line 102 are vertically intersected, and the touch driving electrode 103 is parallel to the gate line 101 and perpendicular to the data line 102 .

[0050] In order to avoid the signal delay of the touch driving electrodes 103, the array substrate further includes: a third conductive line 106 arranged in the same layer and the same material as the data line 102, the third conductive line 106 is arranged in parallel with the data line 102, That is, it is vertically arranged w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com