Chip adaptive configuration method and device

A chip configuration, self-adaptive technology, applied in the direction of measuring devices, instruments, measuring electronics, etc., can solve the problems of increased material risk, unfavorable control of material cost, and narrowed range of material chips, so as to improve matching and reduce The effect of exclusive material risk and equipment stability improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described below are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

[0049] Figure 4 It is a flow chart of the method for adaptively configuring the chip provided by the present invention, such as Figure 4 As shown, the steps include:

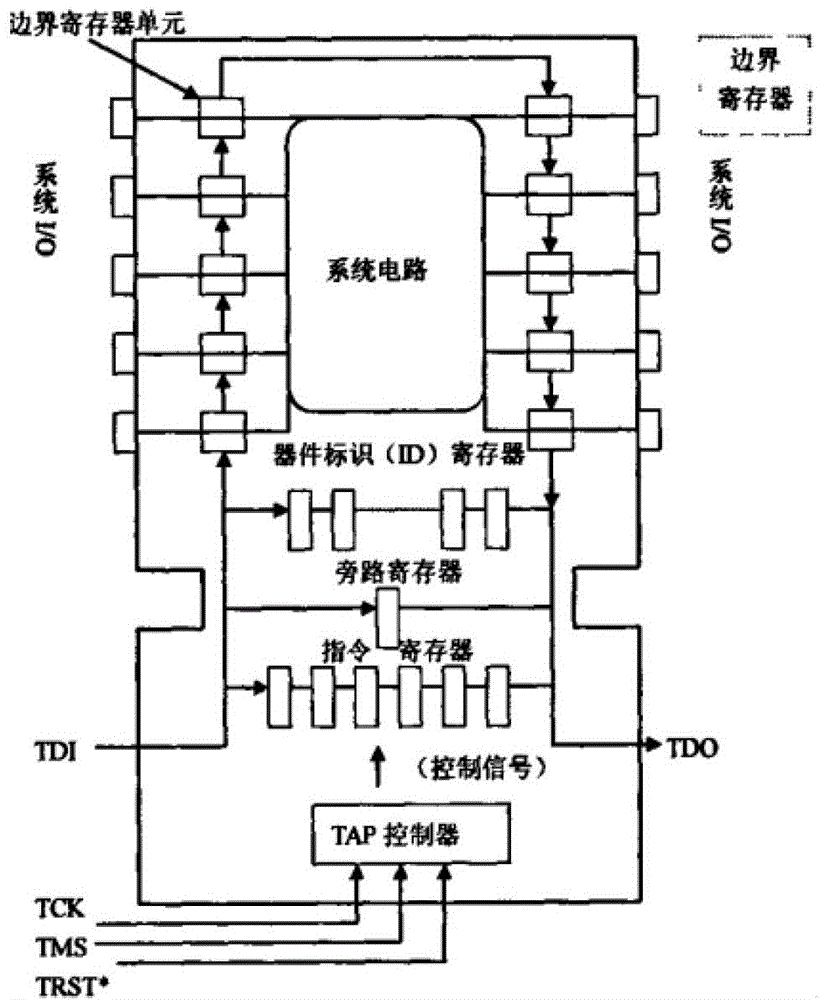

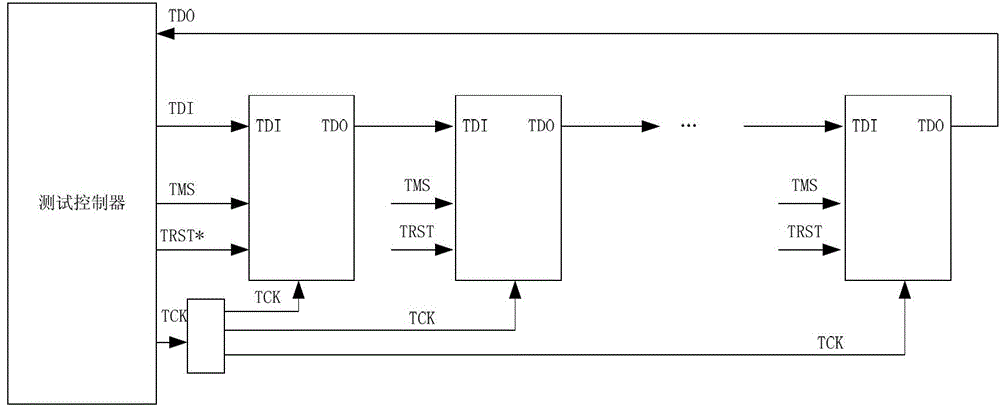

[0050] Step 401: when the chip is powered on, the test controller controls each chip to be identified to be in a scanning mode through a test link connected to each chip to be identified.

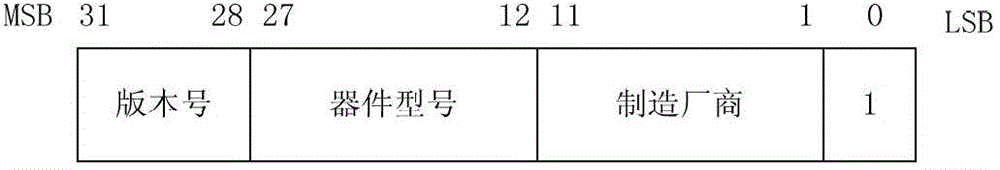

[0051] Step 402: The test controller scans the device identification register of each chip to be identified through the test link to identify and read out the chip model.

[0052] Step 403: After acquiring the chip model of each chip to be identified, the test controller controls the chip to be identif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com