Heterojunction solar cell with selective emitting electrode and manufacturing method thereof

A solar cell and emitter technology, applied in photovoltaic power generation, circuits, electrical components, etc., can solve the problems of high doping concentration, reduced passivation effect, reduced open-circuit voltage and short-circuit current, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

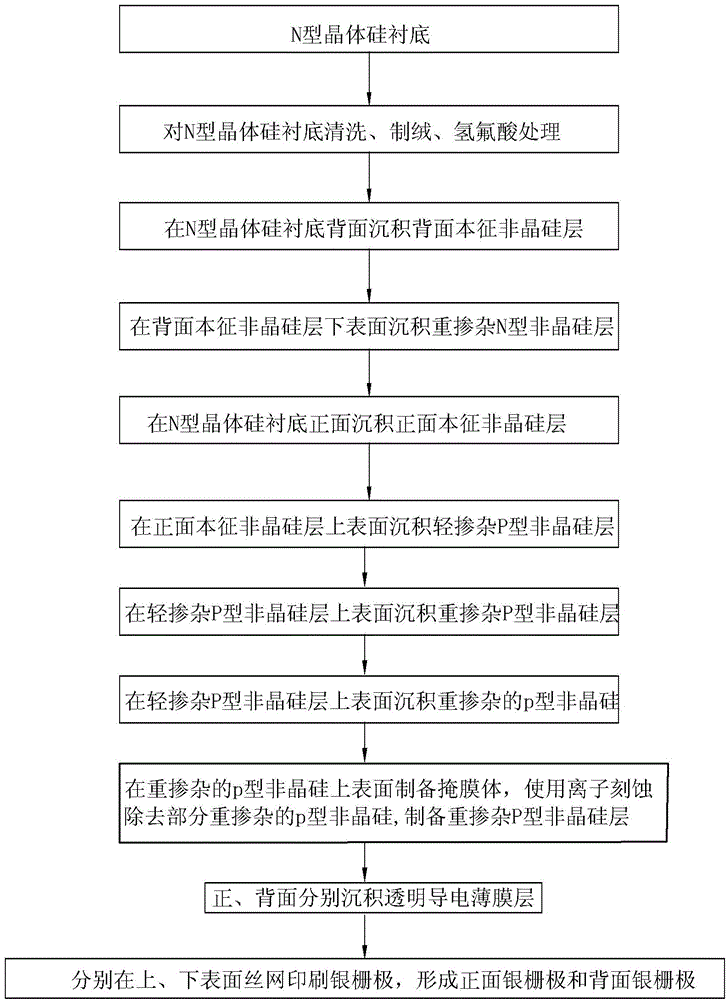

[0023] like figure 1 As shown, a heterojunction solar cell with a selective emitter, which includes:

[0024] An N-type crystalline silicon substrate 1, which has a front side and a back side;

[0025] A front intrinsic amorphous silicon layer 2 deposited on the front surface of the N-type crystalline silicon substrate 1;

[0026] A lightly doped P-type amorphous silicon layer 3 deposited on the upper surface of the front intrinsic amorphous silicon layer 2;

[0027] A front transparent conductive film layer 4, located on the upper surface of the lightly doped P-type amorphous silicon layer 3;

[0028] A front silver grid 5, located on the upper surface of the front transparent conductive film layer 4;

[0029] A heavily doped P-type amorphous silicon layer, used as a selective emitter, is arranged on the contact portion between the front transparent conductive film layer 4 and the lightly doped P-type amorphous silicon layer 3, which has a plurality of heavily doped P-type...

Embodiment 2

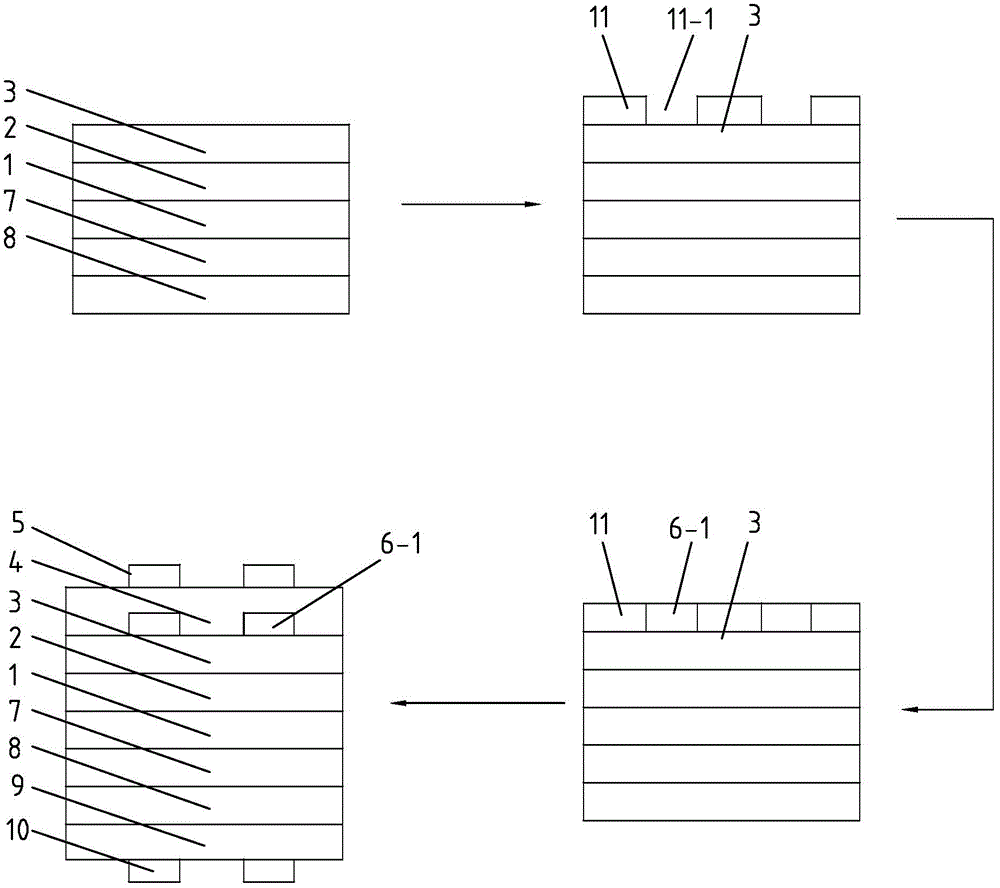

[0037] like image 3 , 4 As shown, the final structure of the heterojunction solar cell with a selective emitter in Example 2 is the same as that of Example 1, the difference is its preparation method, and the preparation method in Example 2 is as follows: N with a thickness of about 200 microns N-type crystalline silicon is cleaned by standard RCA, textured and HF acid dip treatment, and a layer of intrinsic amorphous silicon layer 7 on the back is deposited by PECVD process on the back, with a thickness of 3-15nm, to passivate the N-type crystalline silicon substrate 1 reduce the surface recombination rate, and then deposit a layer of heavily doped n+-a-Si:H, with a typical thickness of 3-20nm, to form a heavily doped N-type amorphous silicon layer 8, on the N-type crystalline silicon lining Deposit a layer of intrinsic amorphous silicon layer 2 on the front side of the bottom 1 through PECVD process, with a thickness of 3-15nm, passivate the front side of the N-type crysta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com