Reconfigurable rapid parallel multiplier

A multiplier and fast technology, applied in the field of fast parallel multipliers, can solve problems such as long calculation time and unsuitable for high-speed applications, and achieve the effect of reducing calculation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

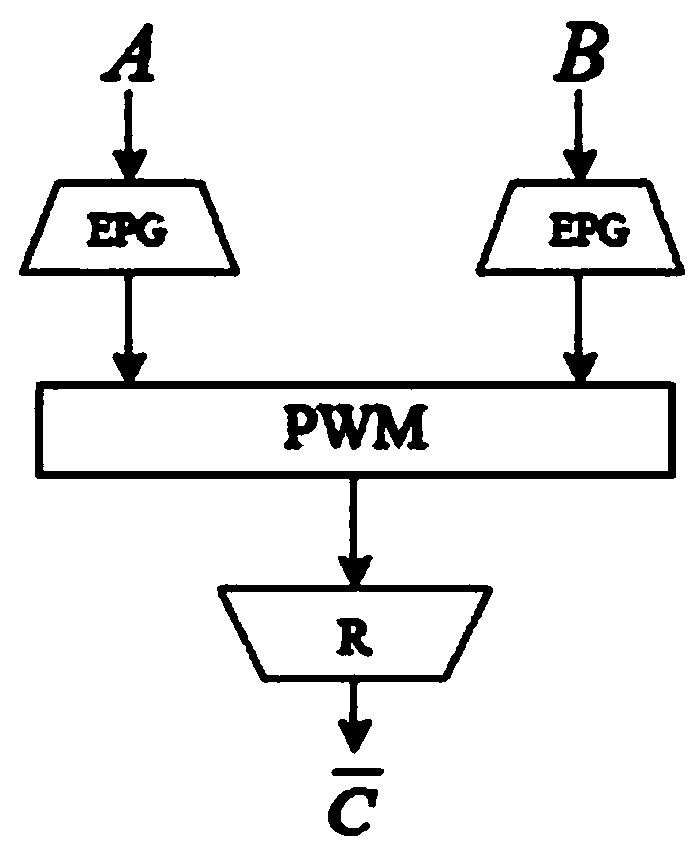

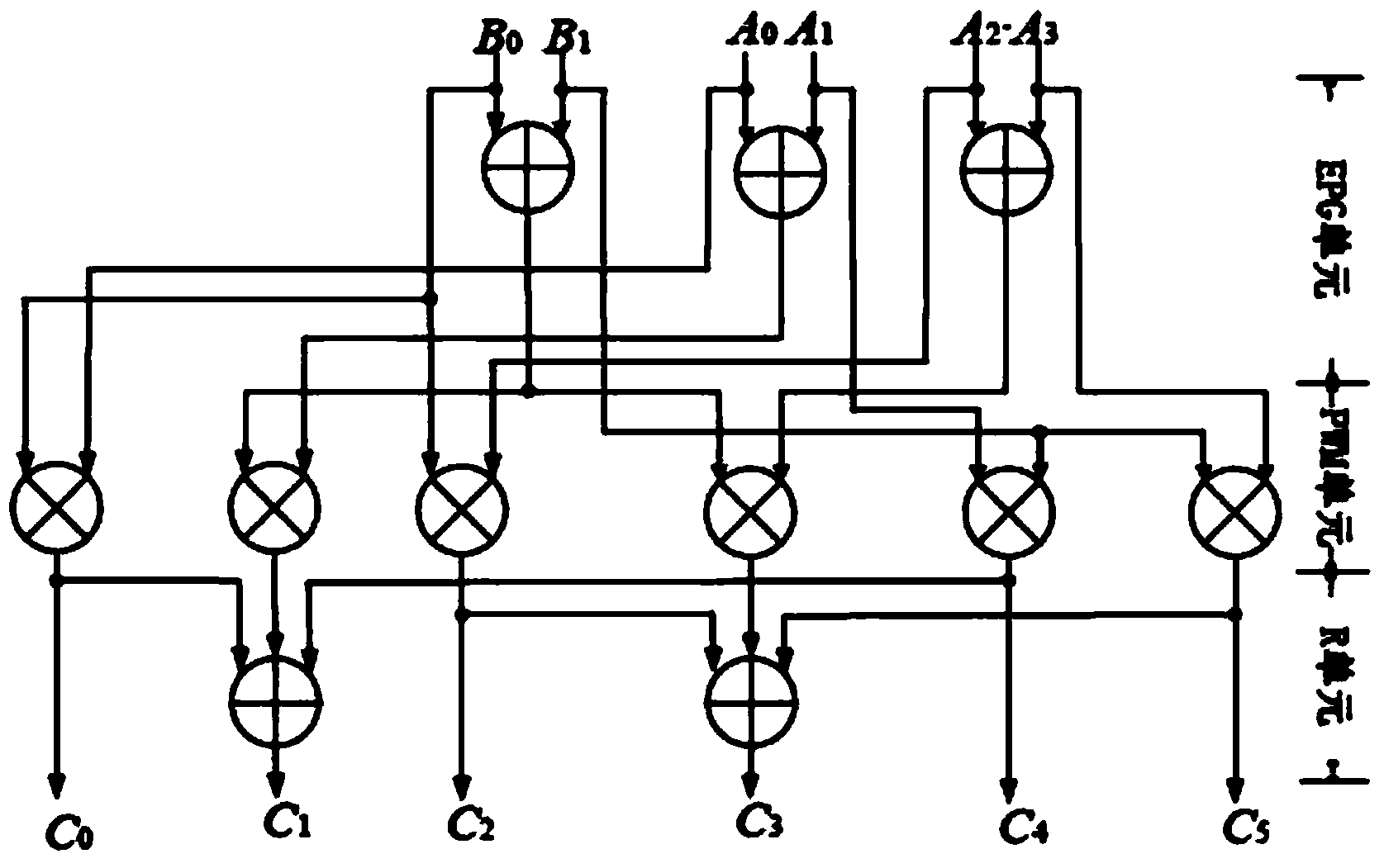

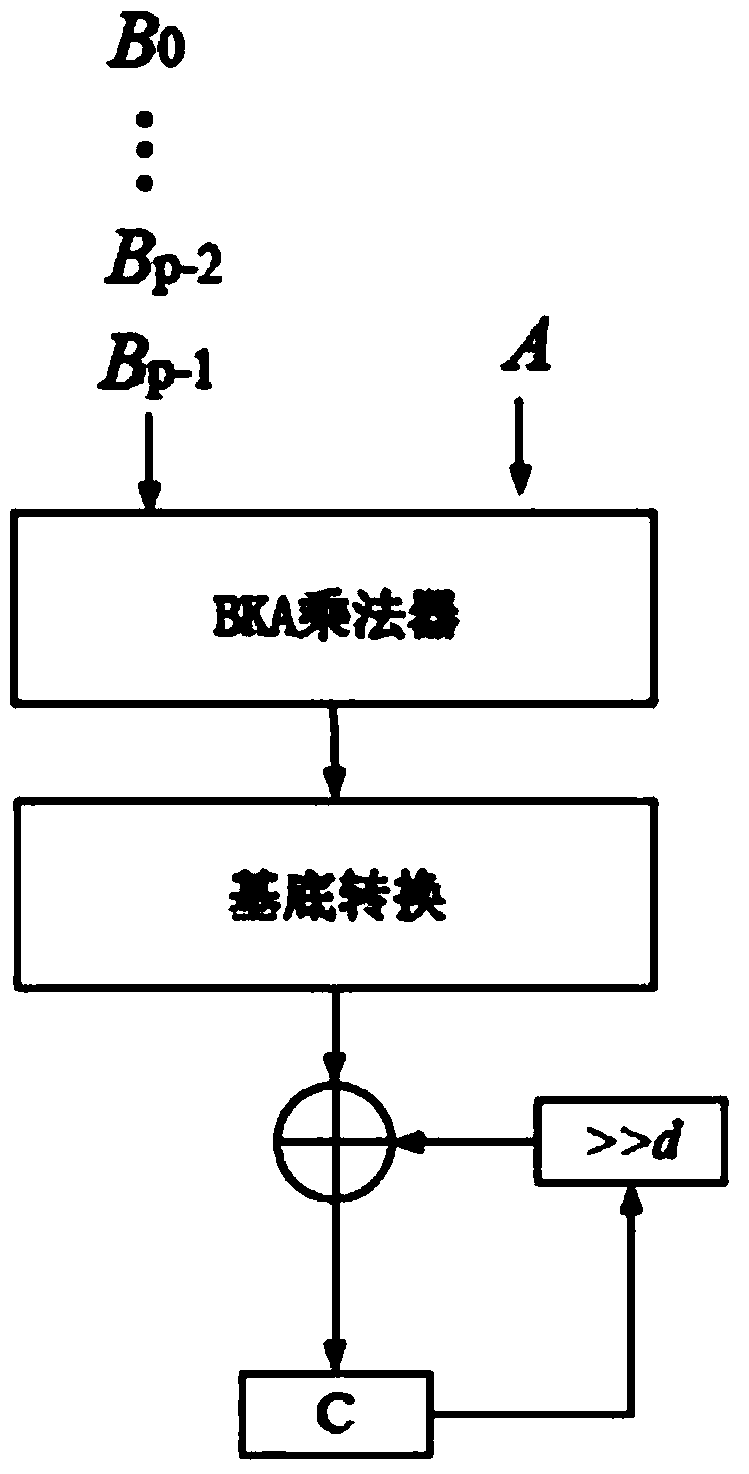

[0021] Use attached figure 1 The shown multi-way KA (Karatsuba Algorithm) and (b, 2)-way BKA (Bivariate Karatsuba Algorithm) algorithm to obtain GF(2 m ) on a reconfigurable multiplier, where the elements on the domain are represented by SPB (Shifted polynomial basis). Set the element on the domain Can be expressed as A=A 0 +A 1 x n +A 2 x 2n ,in

[0022] and A i =a i,0 +a i,1 x+...a i,n-1 x n-1 , 0≤j≤n-1. Let GF(2 m ) consists of an irreducible polynomial F(x) of degree m. For A, B∈GF(2 m ), product C=x -v ABmodF(x) can be expressed as:

[0023] C=x -v [A 0 B 0 +(A 0 B 0 +A 1 B 1 +A 01 B 01 )x n +(A 0 B 0 +A 1 B 1 +A 2 B 2 +A 02 B 02 )x 2n +(A 1 B 1 +A 2 B 2 +A 12 B 12 )X 3n +A 2 B 2 x 4n ]modF(x)=x -v [A 0 B 0 (1+x n +x 2n )+A 1 B 1 (x n +x 2n +x 3n )+A 2 B 2 (x 2n +x 3n +x 4n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com