TFT array substrate, display panel and manufacturing method of display panel

A technology for array substrates and display panels, which is used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of increasing manufacturing cost and process complexity, and cannot meet high aperture ratios, and achieves lower manufacturing costs and The complexity of the process, the high aperture ratio, and the effect of satisfying the aperture ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

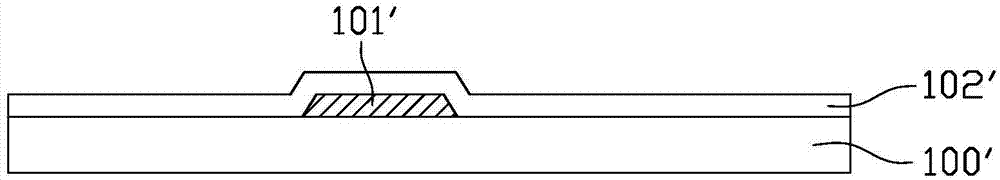

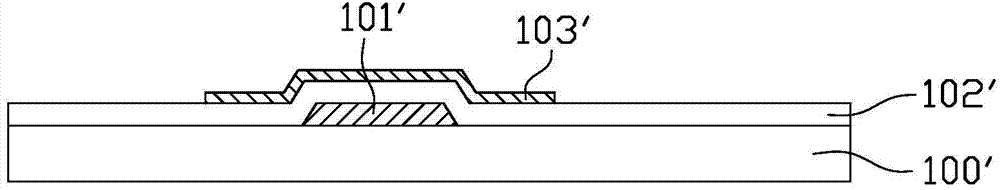

[0042] Figure 2a It is a partial cross-sectional schematic diagram of the TFT array substrate according to the first embodiment of the present invention. Figure 2b It is a partial plan view of the TFT array substrate according to the first embodiment of the present invention. Please also see Figure 2a and Figure 2b The TFT array substrate includes a gate metal layer 101, a gate insulating layer 102, a semiconductor layer 103, a source / drain metal layer 104, a first protective layer 105, a flat layer 106, a pixel electrode 107, The second protective layer 108 and the common electrode 109 . Wherein, the source / drain metal layer 104 includes a source metal layer 1041 and a drain metal layer 1042, the source metal layer 1041 and the drain metal layer 1042 are separated from each other and located in the same layer, and are arranged between the gate metal layer 101 and the semiconductor layer. 103 is in contact with the semiconductor layer 103 , so that a part of the semico...

no. 2 example

[0068] Figure 4 It is a partial cross-sectional schematic diagram of a TFT array substrate according to the second embodiment of the present invention. Such as Figure 4 The TFT array substrate shown with Figure 2aThe difference of the TFT array substrate shown is that the semiconductor layer 103 is indium gallium zinc oxide (IGZO), and the TFT array substrate further includes an etching stopper layer 203 disposed on the semiconductor layer 103 . Compared with amorphous silicon (a-si), IGZO has the characteristics of high mobility and good uniformity, so it can better realize large-size high-resolution panels. In addition, IGZO also has the characteristic of low leakage current, therefore, IGZO can also reduce power consumption as the semiconductor layer 103 . Simultaneously, because IGZO is more sensitive to water, oxygen, therefore adopt IGZO as semiconductor layer 103, it may be polluted easily and change molecular structure and become conductor or insulator material, ...

no. 3 example

[0072] Figure 8 It is a partial cross-sectional schematic diagram of the TFT array substrate according to the third embodiment of the present invention. The present invention as Figure 8 The TFT array substrate shown with Figure 2a The structure of the TFT array substrate shown is basically the same, the difference is that the via hole 110 formed by etching the first protective layer 105 using the patterned flat layer 106 as a photoresist mask is located at the gate metal layer 101 and the drain electrode. Above the metal layer 1042, so compared with the first and second embodiments, the via hole 110 of this embodiment does not need to be formed in the light-transmitting region of the TFT array substrate, so that the pixel electrode 107 is in contact with the drain metal 1042, so This embodiment further increases the aperture ratio.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com