Assembly line successive approximation type analog-digital converter self-calibration method and device

An analog-to-digital converter, successive comparison technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve the problems of operational amplifier offset and difficult to achieve, and achieve the effect of improving the effective accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

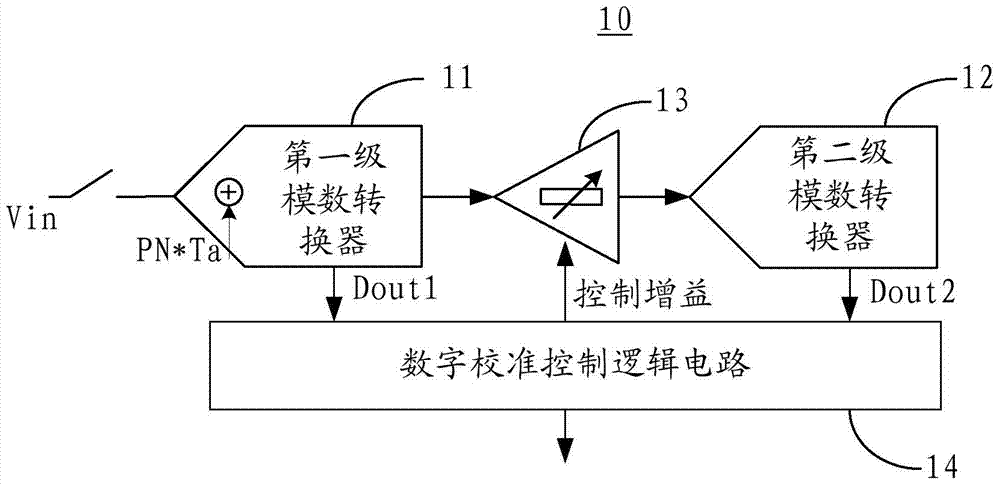

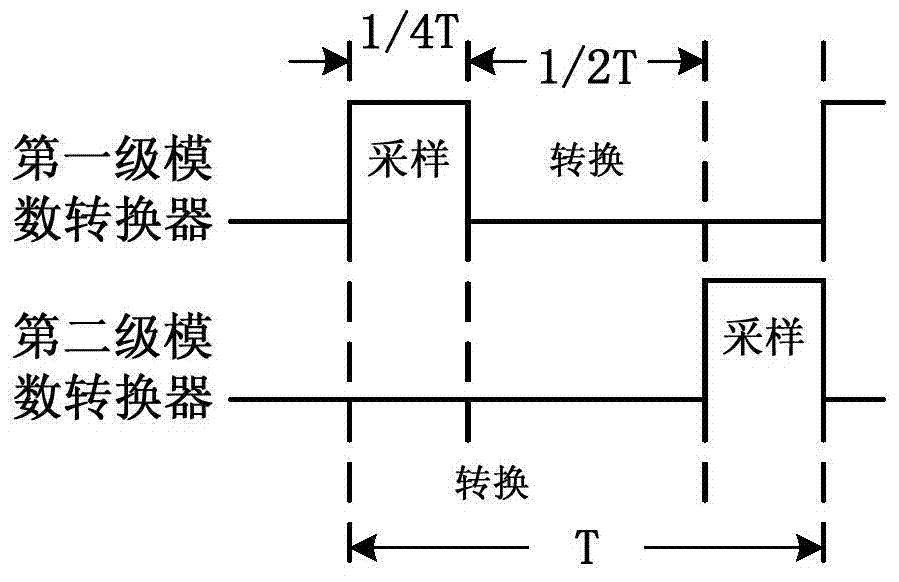

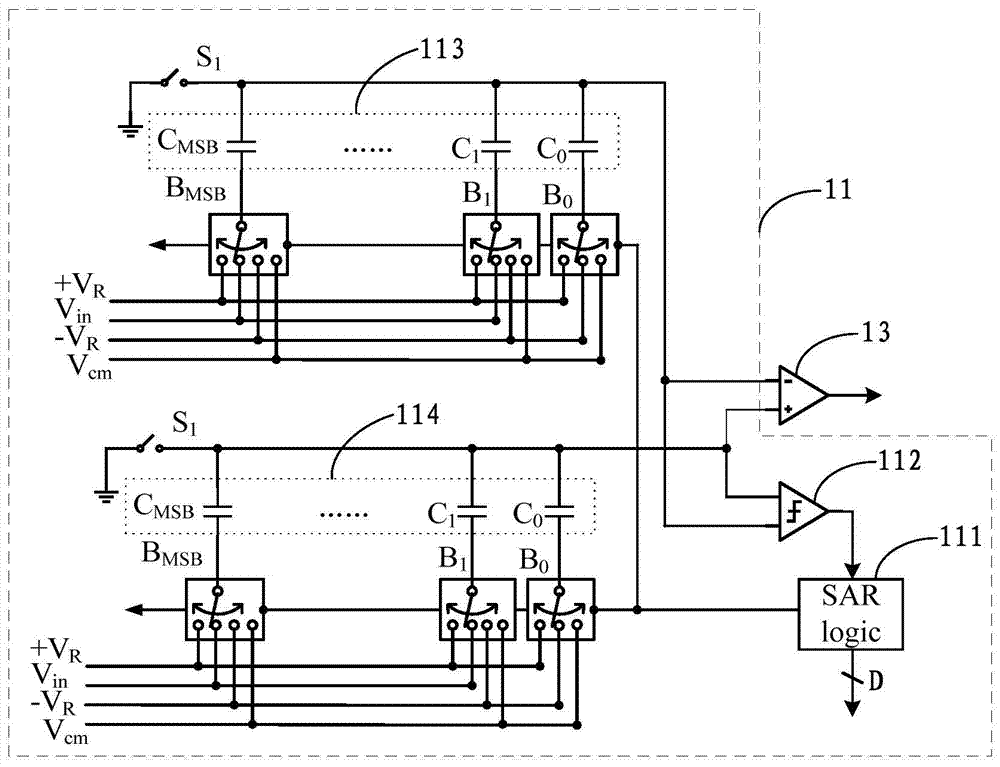

[0054] See figure 1 , figure 1 It is a structural schematic diagram of the self-calibration device of the pipeline successively comparing analog-to-digital converters according to the first embodiment of the present invention. Such as figure 1 As shown, the self-calibration device 10 of the pipeline successive comparison analog-to-digital converter includes: a first-stage successive approximation analog-to-digital converter 11, a second-stage successive approximation analog-to-digital converter 12, an operational amplifier 13, and a digital calibration control logic circuit 14. Dout1 is the output after analog-to-digital conversion by the first-stage successive approximation analog-to-digital converter 11 , and Dout2 is the output after analog-to-digital conversion by the second-stage successive-approximation analog-to-digital converter 12 . The o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com