NCS algorithm parallelization method based on multiple FPGA platforms

An algorithm and platform technology, applied in the field of parallelization of NCS algorithms, can solve the problems of low computing efficiency, high memory read speed and high processor performance requirements, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The solution of the present invention will be described in detail below in conjunction with the accompanying drawings.

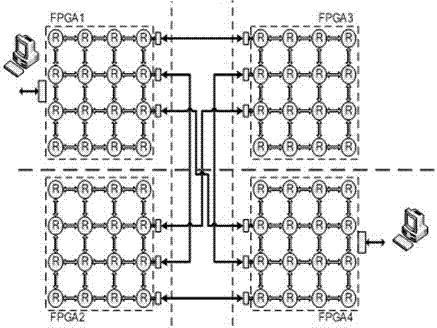

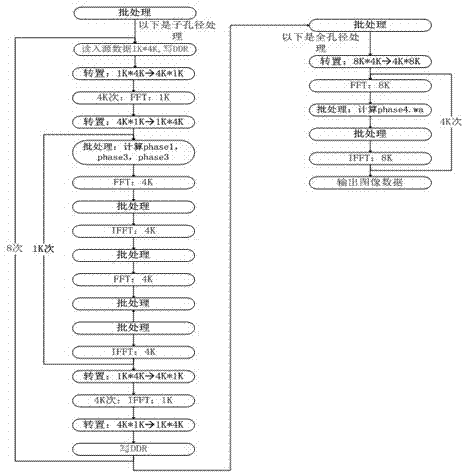

[0023] This embodiment is based on a multi-FPGA platform composed of 4 Xilinx XC6VLX550T FPGA chips, such as figure 1 As shown, each FPGA chip is designed with a heterogeneous multi-core prototype chip based on 4*4 2D mesh architecture, the data bit width is 64 bits, and the 4*4 2D mesh architecture is expanded to 16*16 2D mesh through the high-speed channel between FPGAs architecture. Each FPGA chip integrates 4 computing cluster units and 1 transposition cluster unit to complete a large number of calculations and transpositions in the NCS algorithm. The overall software flow of the NCS algorithm is as follows: figure 2 shown. In the following, combined with the NCS algorithm, taking an image scale with a data volume of 32M Byte as an example, the pipeline method and task parallelization method will be described in detail.

[0024] The method fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com