Integrated circuit floor planning method based on moving modal sequence and Memetic algorithm

A mobile pattern sequence, integrated circuit technology, applied in the direction of genetic model, can solve the problems of poor stability, slow convergence, unable to obtain project schedule and other problems, achieve good implicit parallelism, ensure effective search, and avoid local optimality. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

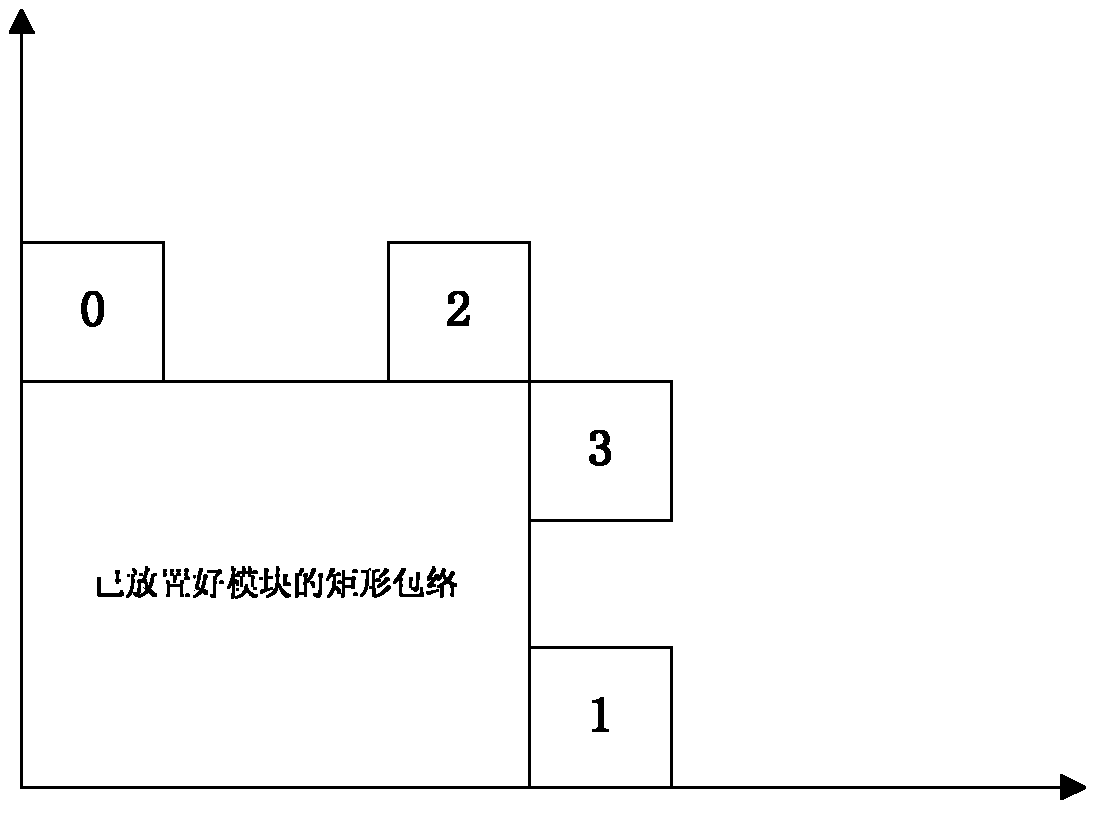

[0058] The layout method studied by the present invention is to determine the position of the hard module on the chip, so that certain performances of the chip, such as the chip area and the total length of interconnection lines between modules, can be optimized. The present invention solves how to place modules, and aims at minimizing the area of the chip, and tests the standard question bank MCNC Benchmark.

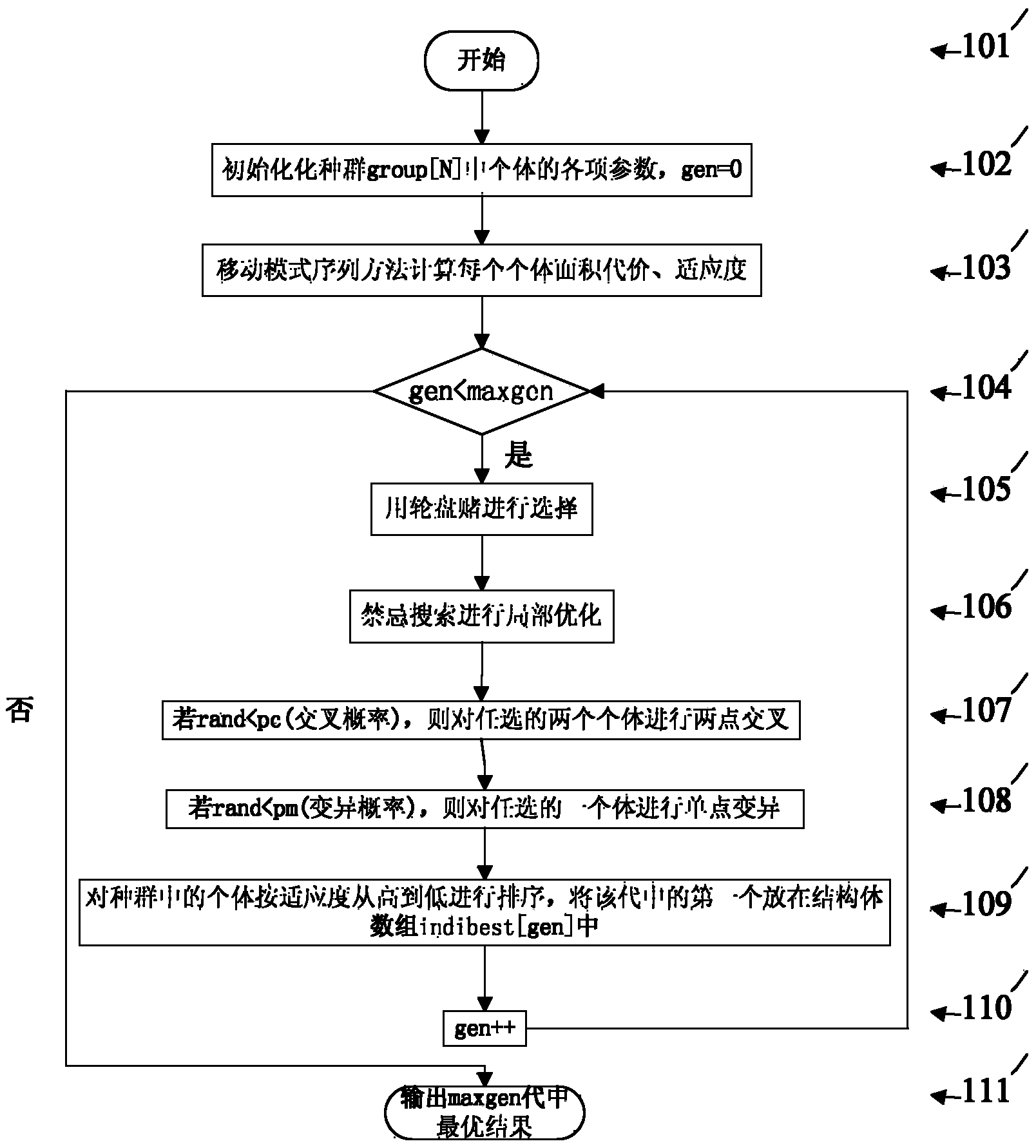

[0059] Such as figure 2 as shown,

[0060] The main flowchart step features are:

[0061] Step 101: start parameter setting, N is the number of populations in the genetic algorithm, M is the number of individuals in each population, H is a constant (here set to 100), which is used to divide by the cost value of each individual area, so that Get the individual fitness. RX and RY respectively represent the maximum value of the abscissa and the maximum value of the ordinate in the two-dimensional plane where the rectangular module is placed. T represents the number ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com