Very large scale integration (VLSI) standard unit overall arranging method based on L1 form model

A global layout, L1 norm technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as inability to guarantee layout quality, non-smooth density constraint function, bus length error, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0072] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

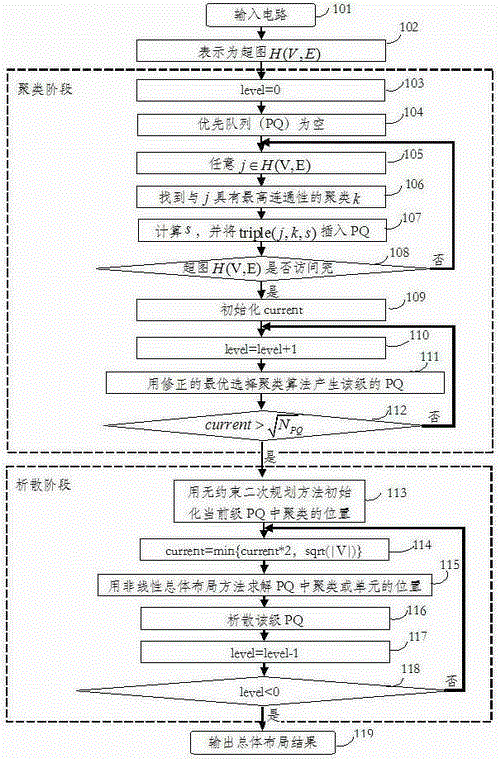

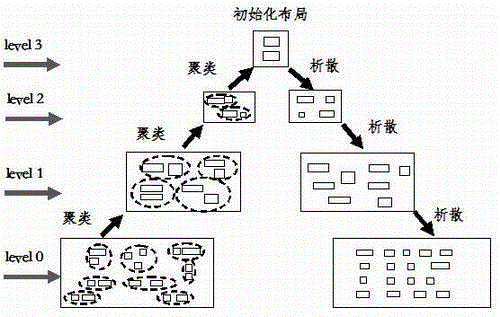

[0073] The present invention is based on the L1 norm model global layout method of VLSI standard cells. Firstly, the circuit is expressed as a hypergraph, and the global layout problem of VLSI standard cells that adopts half-perimeter line length calculation and density constraints is non-smooth is modeled as L1 norm minimization problem, then cells are clustered using a modified optimal choice clustering algorithm for L1-norm models in the clustering phase, followed by clustering in the disintegration phase using a non-linear programming global placement method.

[0074] figure 1 It is a flow chart of the VLSI standard cell global layout method based on the L1 norm model of the present invention. Such as figure 1 Shown, the present invention is based on the VLSI standard cell global layout method of L1 norm model, specifically co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com