AES (advanced encryption standard) algorithm circuit oriented method for testing differential power attack

A differential power consumption attack and testing method technology, which is applied in computing, electrical digital data processing, special data processing applications, etc., can solve the problems of poor reliability, low reliability of results, and difficult implementation, etc. Design, shorten the design cycle, optimize the effect of the design process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with the drawings and specific embodiments.

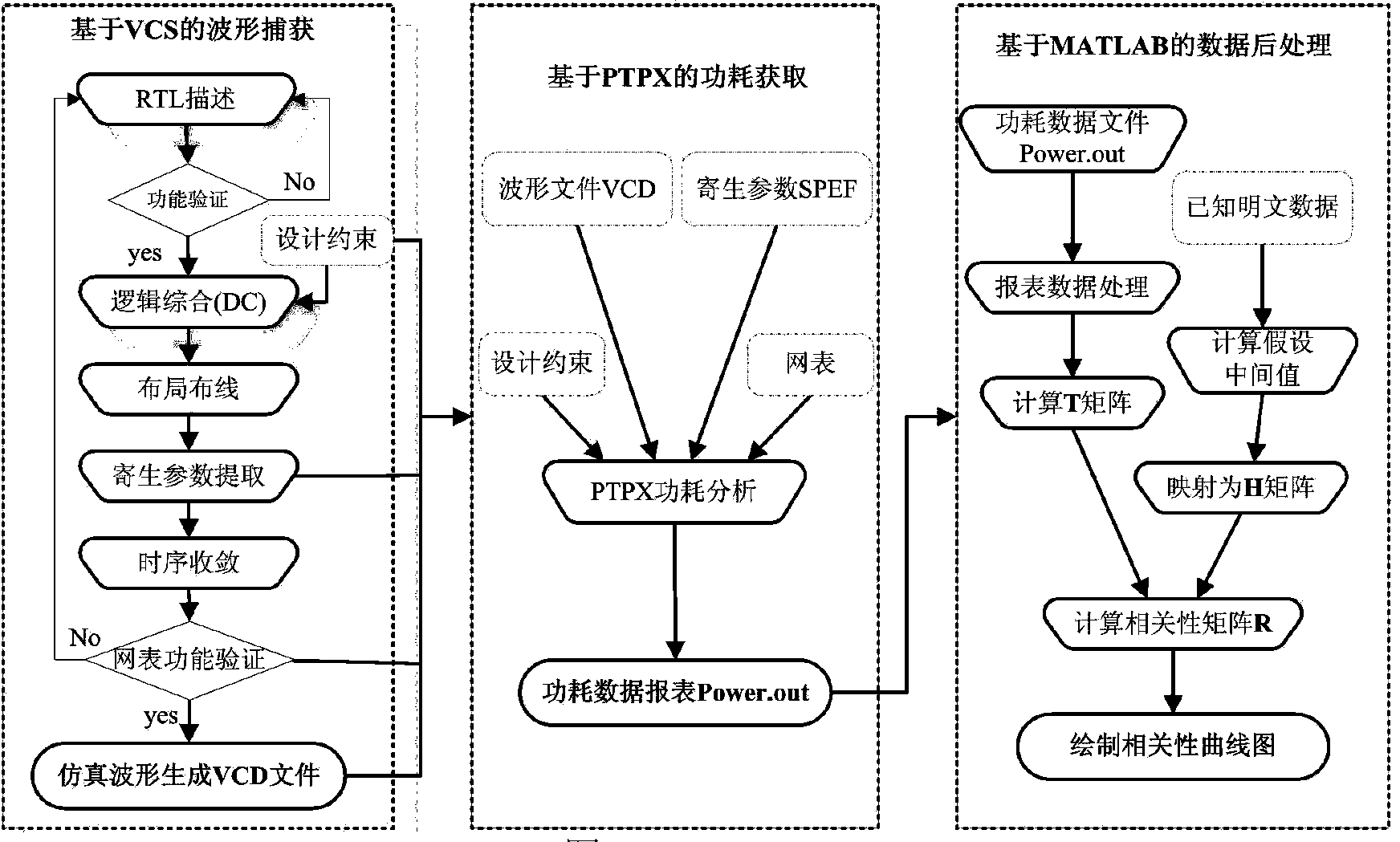

[0037] Such as figure 1 Shown is the overall framework of the differential power attack test method for AES algorithm circuits of the present invention. The core of the AES cryptographic algorithm circuit power attack test method has three parts: functional simulation module, power consumption simulation module and power analysis module. The basic process is to first use the RTL code of the algorithm to synthesize the circuit netlist file through the DC (AESign Compiler, DC) tool, and then load the test vector necessary for the netlist such as plaintext and clock, and the standard cell library and timing parameters used by the netlist Simulate through VCS together to generate functional simulation waveforms. Functional simulation waveforms need to be converted into VCD files for power consumption simulation analysis. Then set the PTPX simulation environment...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com