Multidimensional Histogram Statistical Circuit and Image Processing System

A histogram statistics and histogram technology, applied in the field of image processing, can solve the problems of occupying CPU resources, time-consuming statistical process, poor real-time performance, etc., to achieve the effects of improving real-time performance, avoiding time overhead, and reducing computer power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

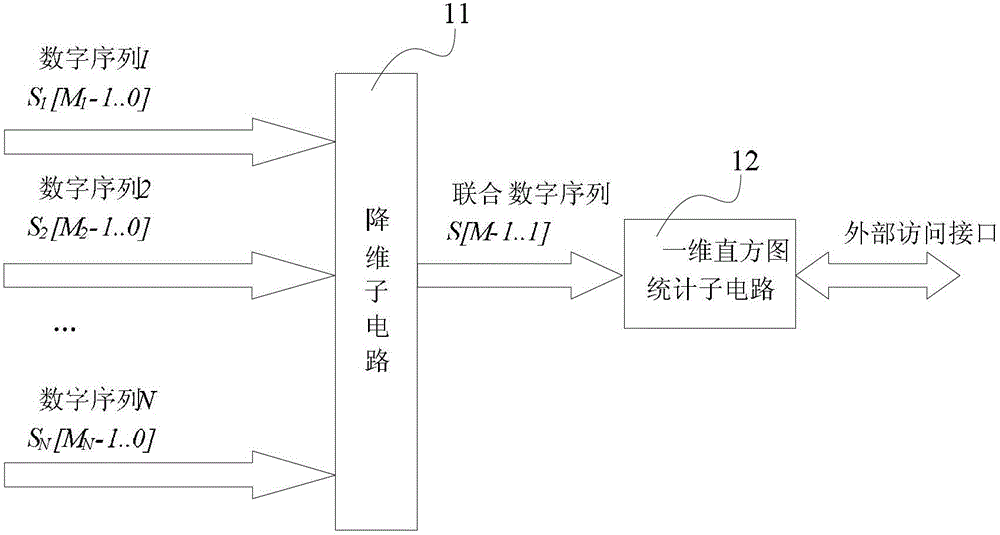

[0037] Please see attached figure 1 , is a schematic structural diagram of a multi-dimensional histogram statistical circuit disclosed in the first embodiment of the present invention, mainly including: a dimensionality reduction sub-circuit 11, a one-dimensional histogram statistical sub-circuit 12 and an external interface circuit (not marked in the figure).

[0038] The dimensionality reduction sub-circuit 11 is mainly used to receive multiple digital sequences corresponding to the multi-dimensional histogram and multi-dimensional vector sample sets, and obtain a joint digital sequence after combining the multiple digital sequences.

[0039] The one-dimensional histogram statistical sub-circuit 12 receives and counts the one-dimensional histogram corresponding to the current joint digital sequence, and determines the data of the multi-dimensional histogram according to the preset data mapping relationship between the one-dimensional histogram and the multi-dimensional histog...

example 1

[0047] When the input is a one-dimensional sequence of N digits with a bit width of Mi, such as figure 1 shown, including the sequence of digits 1S 1 [M 1 -1..0], number sequence 2S 2 [M 2 -1..0] to the numeric sequence NS N [M N -1..0].

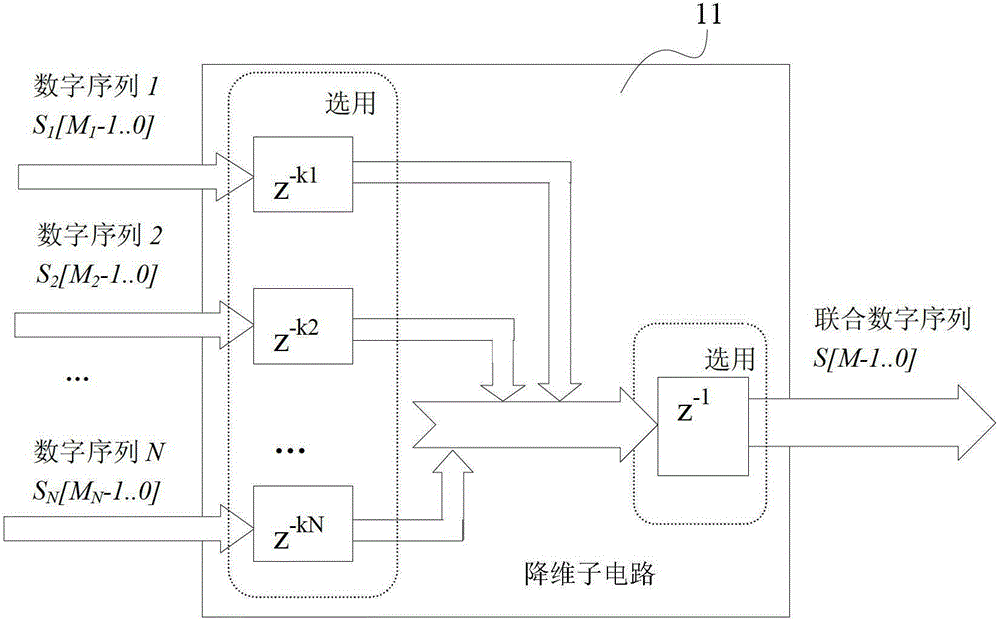

[0048] The dimensionality reduction sub-circuit 11 receives N one-dimensional digital sequences S whose bit width is Mi corresponding to the N-dimensional vector sample set in parallel i [M i -1..0], obtaining the combined digital sequence S[M-1..0] with a bit width of M after merging the N digital sequences as the current combined digital sequence.

[0049] Among them, M and Mi are natural numbers whose bit width is greater than 1; the value range of i is 1~N, N is a natural number greater than 1, and the ".." in the digital sequence is used to represent the bit of parallel digital signal bits, for example, the sequence of digits S 1 [M 1 -1..0] represents the Mth of the digital signal S1 1 From -1 bit to the 0th bit, the digital...

Embodiment 2

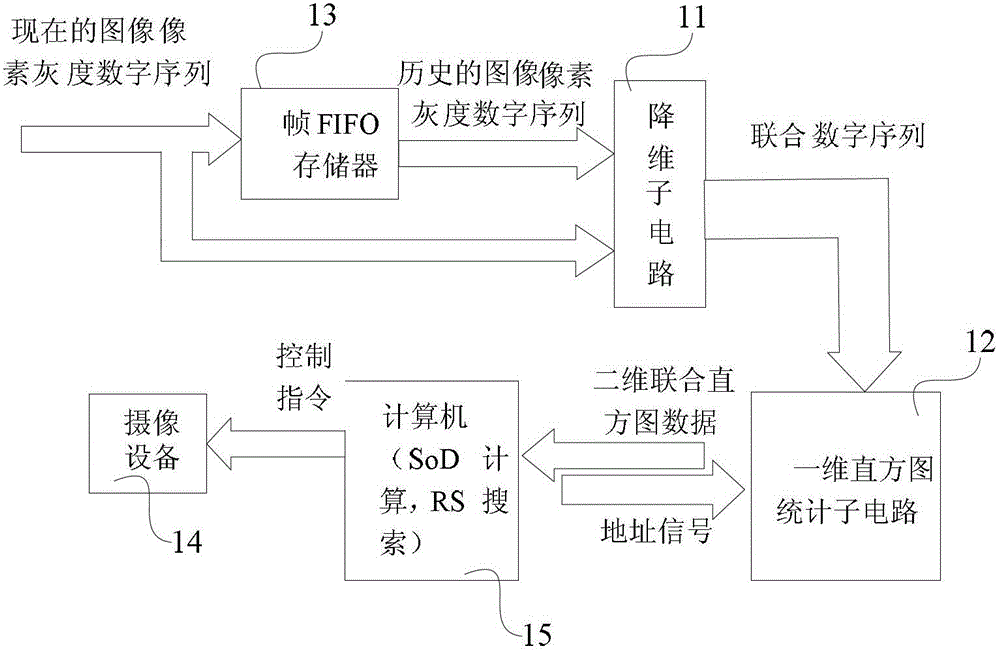

[0071] Based on the multi-dimensional histogram statistical circuit disclosed in the first embodiment of the present invention, when the joint histograms of two adjacent images are counted, as image 3 As shown, the multi-dimensional histogram statistical circuit mainly includes: a frame FIFO memory 13, a dimensionality reduction sub-circuit 11, a one-dimensional histogram statistical sub-circuit 12 and an external interface sub-circuit (not shown in the figure).

[0072] The frame FIFO memory 13 is used to buffer the image pixel grayscale digital sequence collected in the last frame cycle, and as a delay digital sequence S delayed by one cycle 1 [k-1..0] output.

[0073] The dimensionality reduction sub-circuit 11 is used to receive the current image pixel grayscale digital sequence S 2 [k-1..0] and the delayed number sequence S 1 [k-1..0] are combined to obtain the sequence S[2k-1..0] as the current joint digital sequence output.

[0074] The one-dimensional histogram sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com