Chip Thermal Analysis Method Based on 3D Domain Decomposition

A three-dimensional area and thermal analysis technology, which is applied in the fields of instruments, calculations, and electrical digital data processing, can solve problems such as chip errors, the efficiency of chip thermal analysis methods needs to be improved, and the calculation time of chip systems increases.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

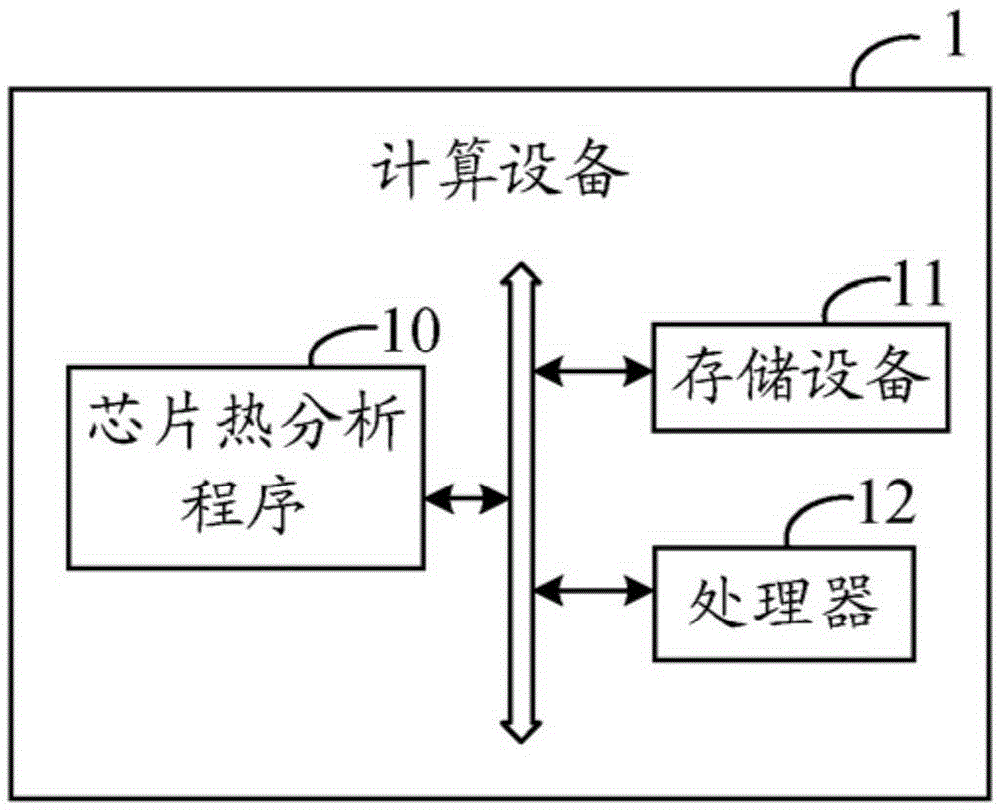

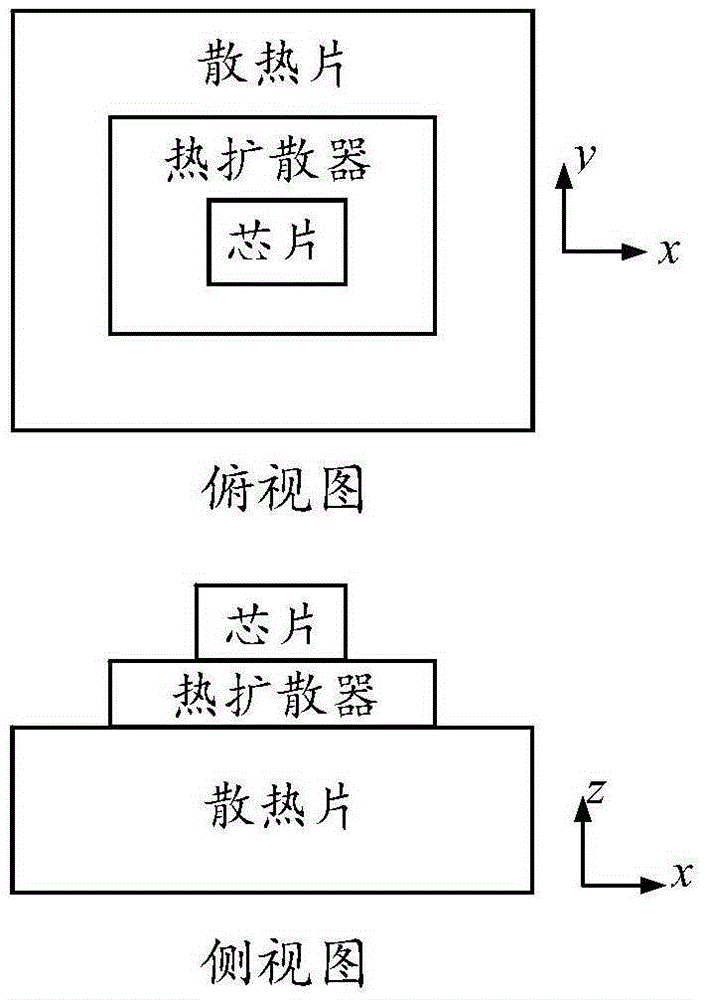

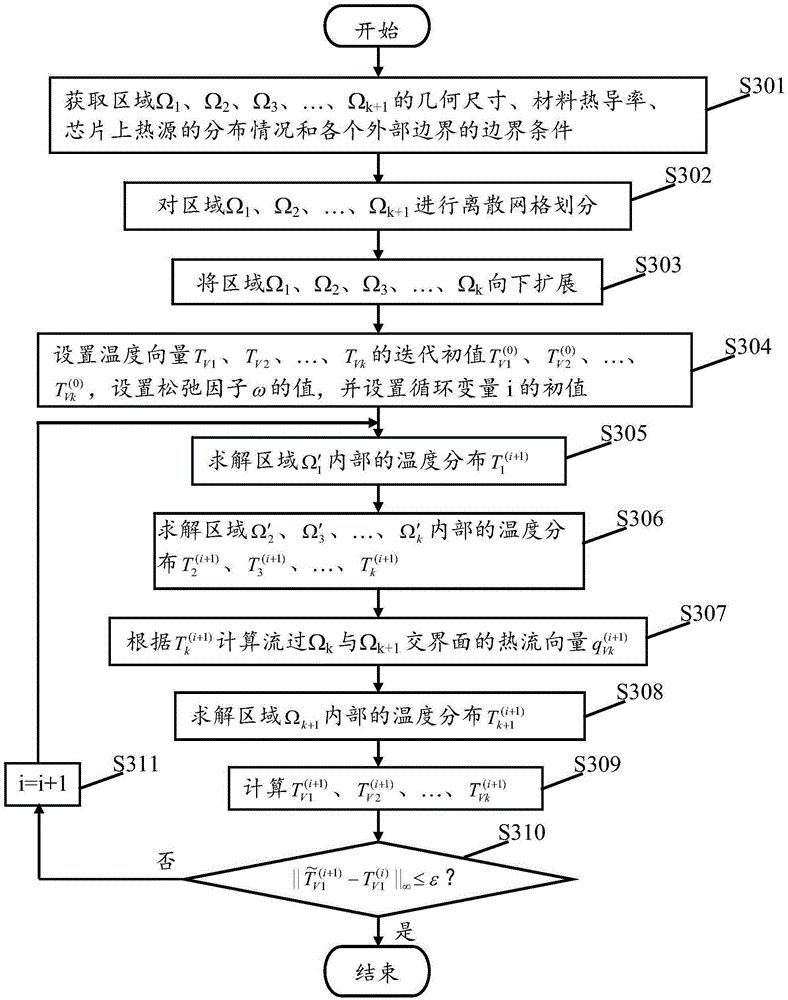

[0017] refer to figure 1 As shown, it is a schematic diagram of the application environment of a preferred embodiment of the chip thermal analysis method based on three-dimensional area decomposition of the present invention. The chip thermal analysis method based on three-dimensional domain decomposition is applied to the computing device 1 . The computing device 1 includes a chip thermal analysis program 10 , a storage device 11 and a processor 12 . The storage device 11 stores program codes of the chip thermal analysis program 10 and data required during operation. The processor 12 executes the program code of the chip thermal analysis program 10 to implement the chip thermal analysis method based on three-dimensional area decomposition, and calculate the temperature distribution of the chip in the chip system. The chip system includes a chip and k heat dissipation components (k≥1). The heat dissipation components include, but are not limited to, heat spreaders and heat ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com