Rapid disconnection control circuit applied to power management circuit

A technology of power management and electrical control, which is applied in the direction of control/regulation system, adjustment of electrical variables, instruments, etc. It can solve problems such as hardware system error, circuit instability state, and low circuit current, so as to avoid logic function or storage error Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

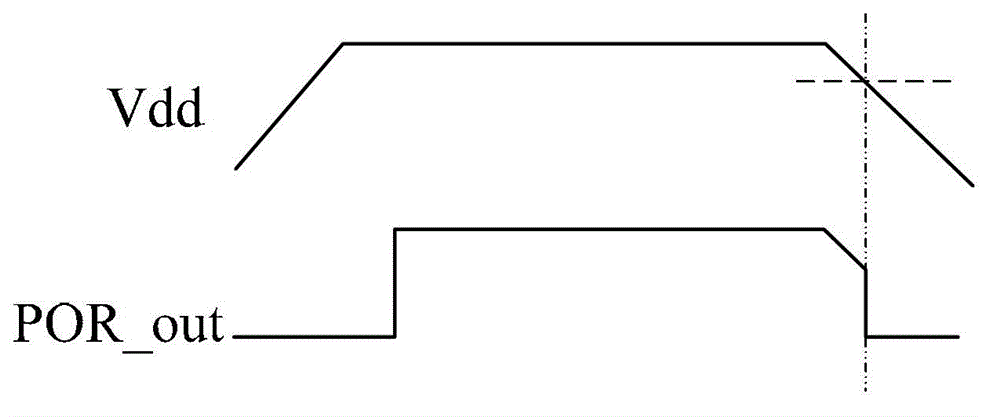

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0019] The invention is applied to a low-dropout linear voltage stabilizing circuit LDO to realize fast power-off.

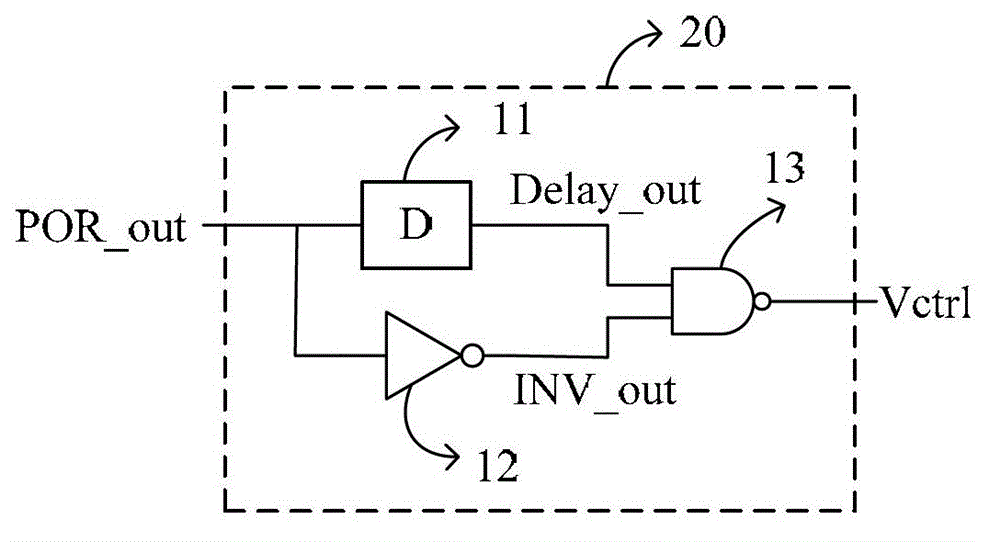

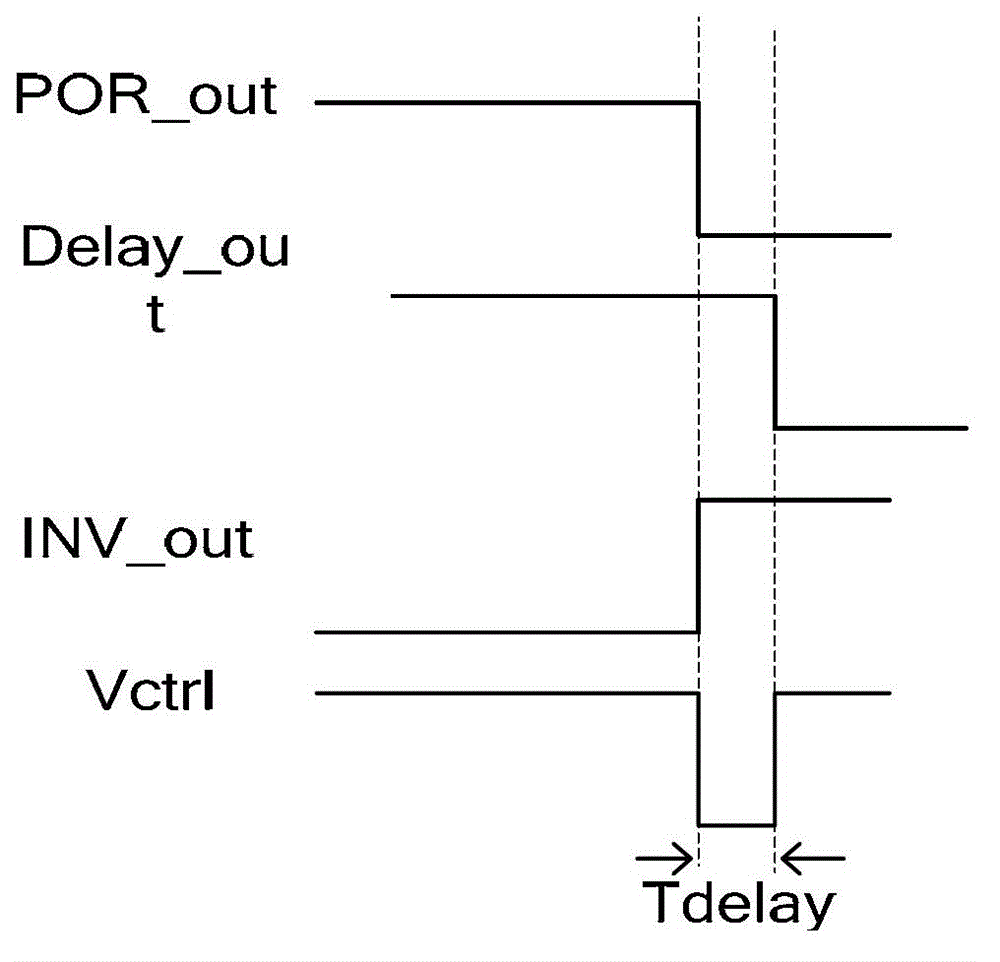

[0020] Such as figure 2 As shown in 4, a fast power-off control circuit 10 used in a power management circuit includes a POR falling edge detection circuit 20 and a PMOS discharge tube Mp2. The POR falling edge detection circuit 20 includes a delay module 11, an inverter The phase converter 12 and the NAND gate 13, the input terminal of the POR falling edge detection circuit 20 is connected to the input terminal of the delay module 11 and the input terminal of the inverter 12, and the output terminal (Delay_out) of the delay module 11 is connected to the inverter 12 The output terminal (INV_out) of the phaser 12 is connected to the two input terminals of the NAND gate 13, and the output terminal (Vctrl) of the POR falling edge detection circuit 20 is connected to the output terminal of the NAND gate 13; the POR falling edge detection circuit 20 The output terminal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com