Growth method of light-emitting diode (LED) epitaxial wafer

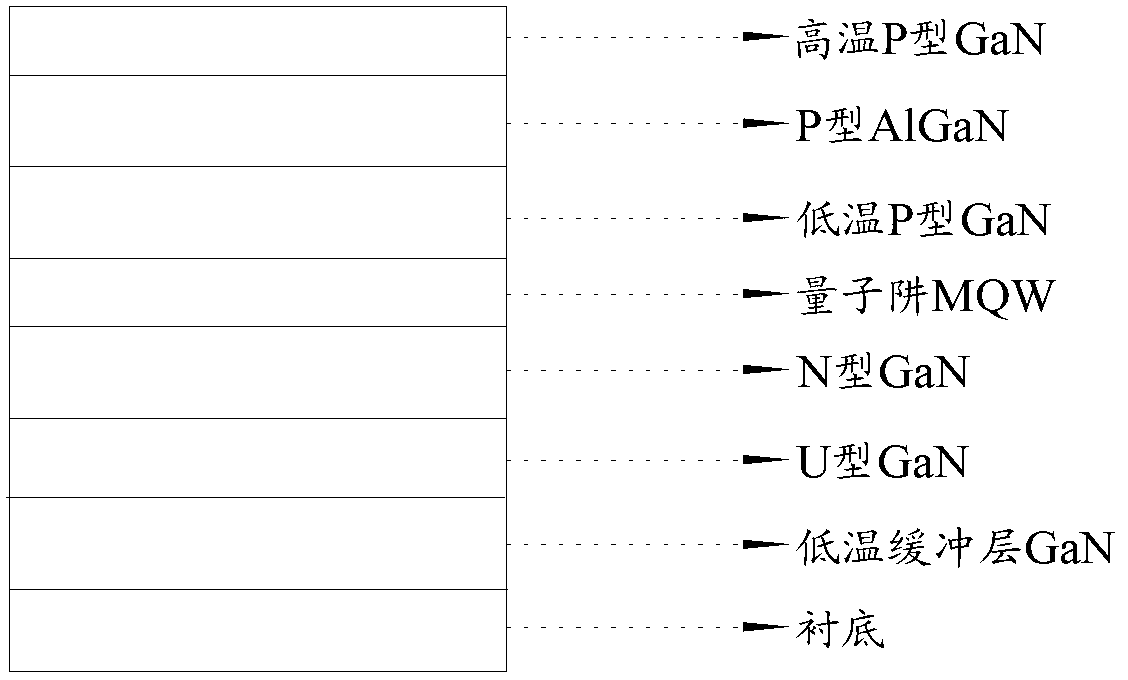

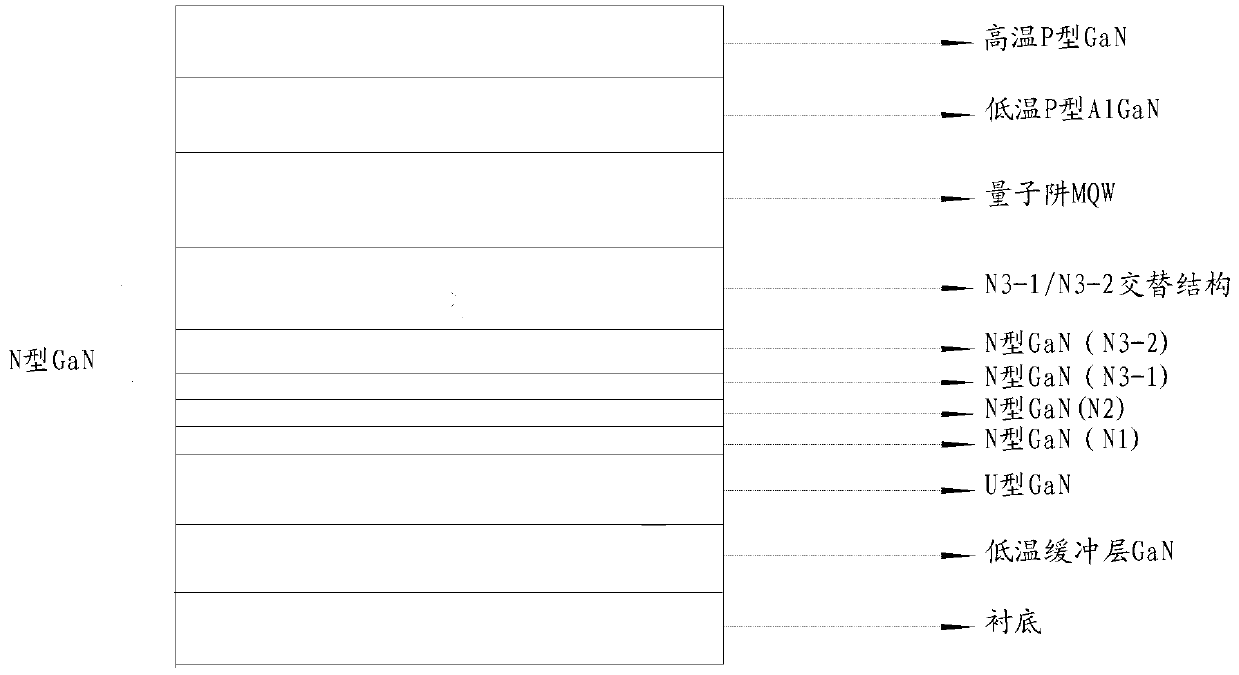

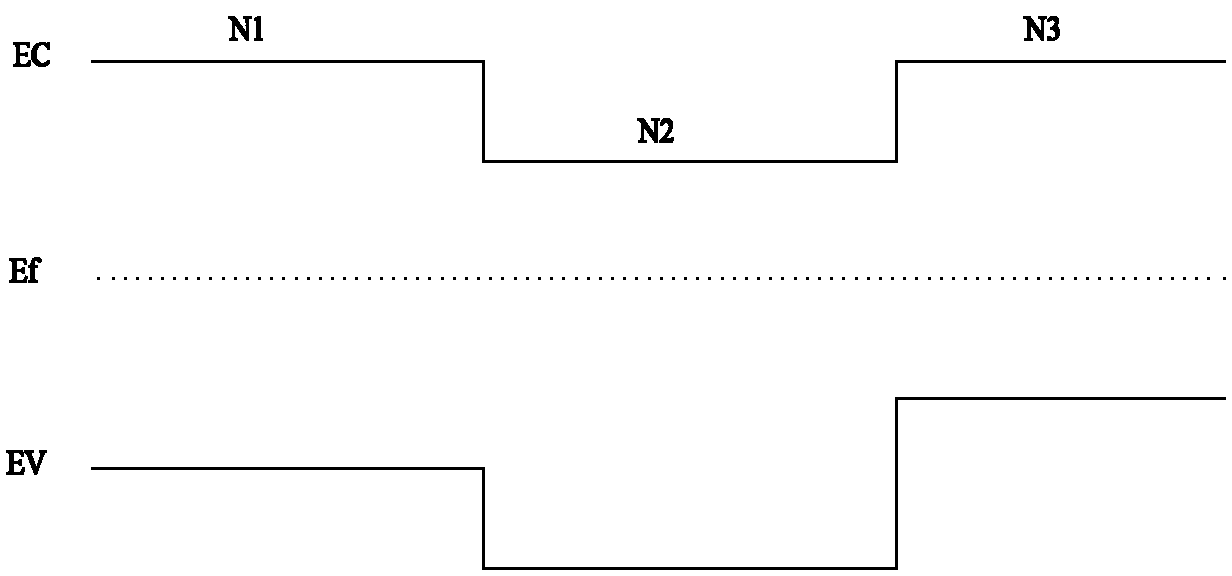

A technology of LED epitaxial wafers and growth methods, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of uneven current distribution of epitaxial layers, high chip voltage, and current congestion, etc., to achieve enhanced electronic horizontal expansion capabilities and save consumption , The effect of reducing the driving voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

[0055] Sample 1 was prepared according to the traditional LED growth method, and sample 2 was prepared according to the method described in the present invention. The difference between sample 1 and sample 2 epitaxial growth method parameters is that sample 2 uses 16 alternate structural layers consisting of N3-1 layer and N3-2 layer alternately grown to replace the N3 layer grown in sample 1. For details, please refer to Table 1 . Sample 1 and sample 2 were plated with 200nm of ITO layer under the same pre-process conditions, 130nm of Cr / Pt / Au electrodes were plated under the same conditions, and the protective layer of SiO was plated under the same conditions. 2 About 50nm, and then grind and cut the sample into chip particles of 762μm×762μm (30mi×30mil) under the same conditions, and then select 150 crystal grains at the same position for sample 1 and sample 2, and package them under the same packaging process. into a white LED. Then an integrating sphere was used to test...

Embodiment approach 2

[0060] Sample 3 was prepared according to the traditional LED growth method, and sample 4 was prepared according to the method described in the present invention. The difference between sample 3 and sample 4 in epitaxial growth method parameters is that sample 4 uses 15 alternate structural layers formed by alternate growth of N3-1 layer and N3-2 layer instead of the N3 layer grown in sample 3. For details, please refer to Table 2 . Samples 3 and 4 were plated with 180nm of ITO layer under the same pre-process conditions, 120nm of Cr / Pt / Au electrodes were plated under the same conditions, and the protective layer of SiO was plated under the same conditions. 2 About 50nm, and then grind and cut the sample into chip particles of 250μm×457μm (10mi×18mil) under the same conditions, and then select 150 crystal grains at the same position for sample 3 and sample 4, and package them under the same packaging process. into a white LED. Then an integrating sphere was used to test the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com