Word line biasing circuit and storage

A word line bias and bias voltage technology, which is applied in the field of memory, can solve problems such as memory cell erasing operation logic confusion, and achieve the effects of reducing GIDL current, avoiding power loss, and weakening the electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

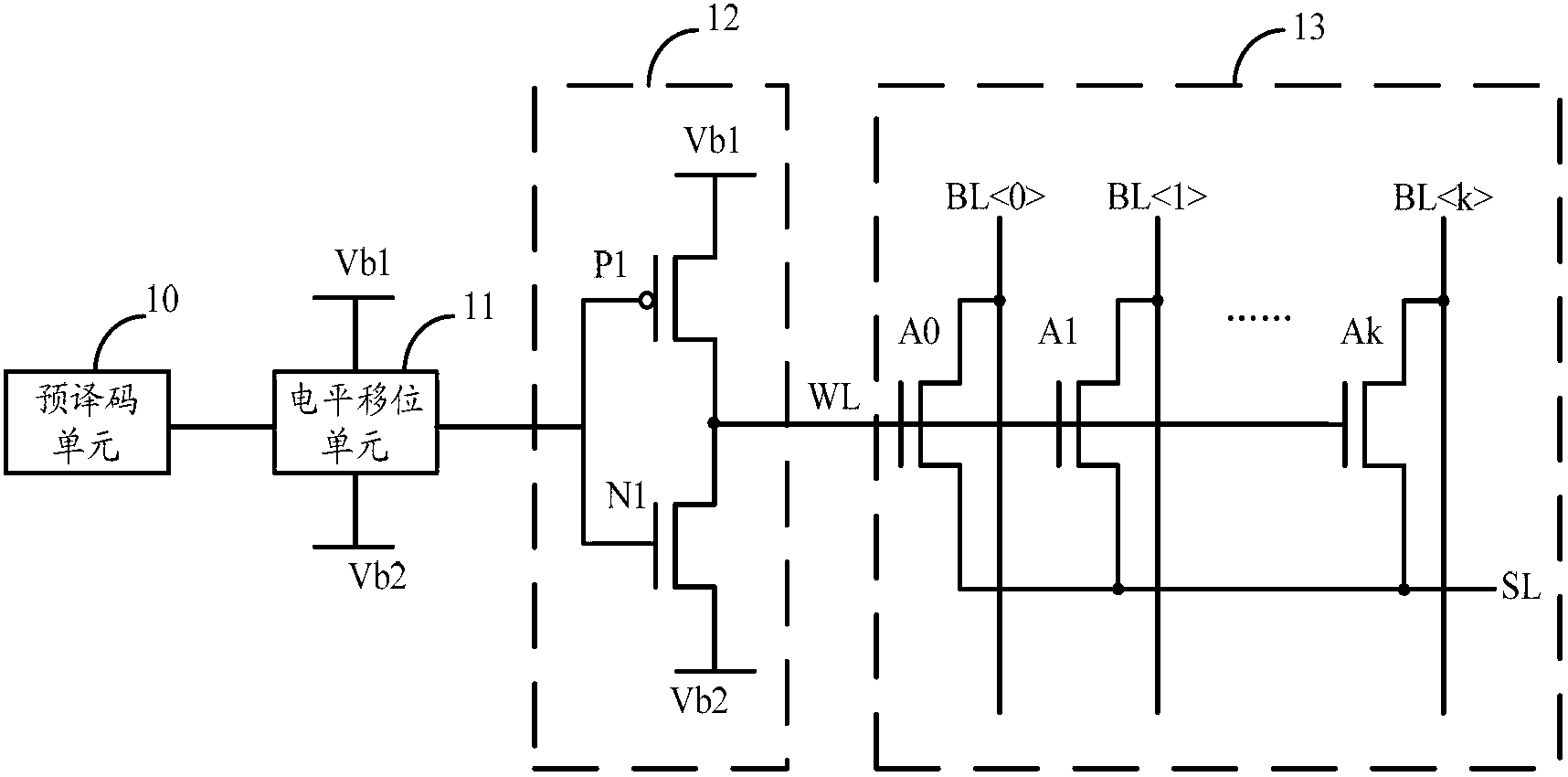

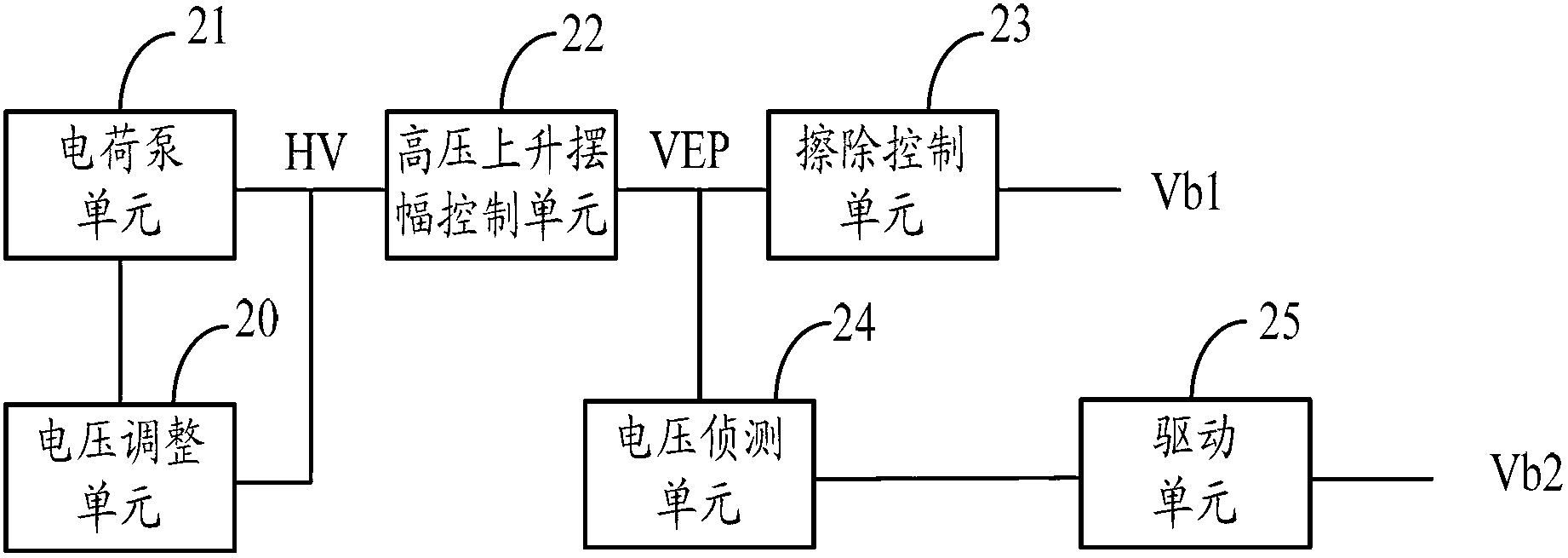

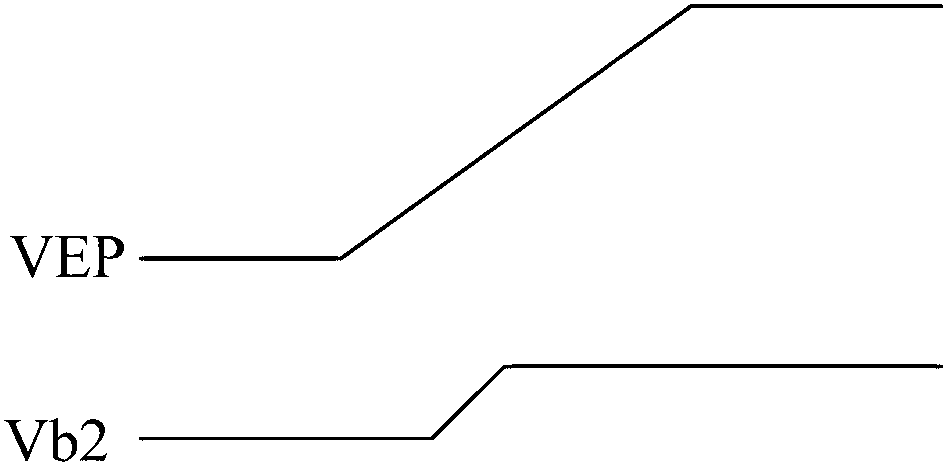

[0027] As described in the background, when performing an erasing operation on a memory cell, the word line driving unit is required to apply a high voltage to the word line, so more GIDL current will be generated in the word line driving unit. Therefore, the inventors of the technical solution consider whether it is possible to reduce the GIDL current by weakening the electric field that generates the GIDL current without excessive power loss of the storage array.

[0028] In order to make the above objects, features and advantages of the present invention more obvious and comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

[0029] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways than those described here, so the present invention...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com