Design method for field programmable analog array (FPAA)-based reconfigurable vector-matrix multiplier

A technology of a matrix multiplier and a design method, which is applied in the calculation using the number system, the calculation using the non-contact manufacturing equipment, and the complex mathematical operation, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

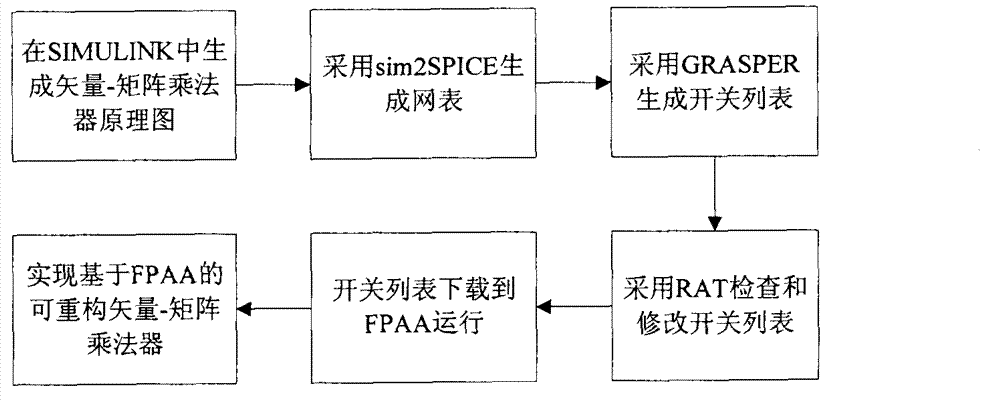

[0017] Below in conjunction with accompanying drawing, the patent of the present invention is described in further detail.

[0018] The mathematical expression of the vector-matrix multiplier is:

[0019] y i = Σ j = 1 n w ij x j , i=1,K,m.

[0020] Among them, w ij is the matrix of multiplicative coefficients, x j is the input vector, y i is the output vector. n is the number of elements in the input vector (corresponding to the number of multiplier input signals), and m is the number of elements in the output vector (corresponding to the number of multiplier output signals). The vector-matrix multiplier operation is actually a multiply-accumulate process.

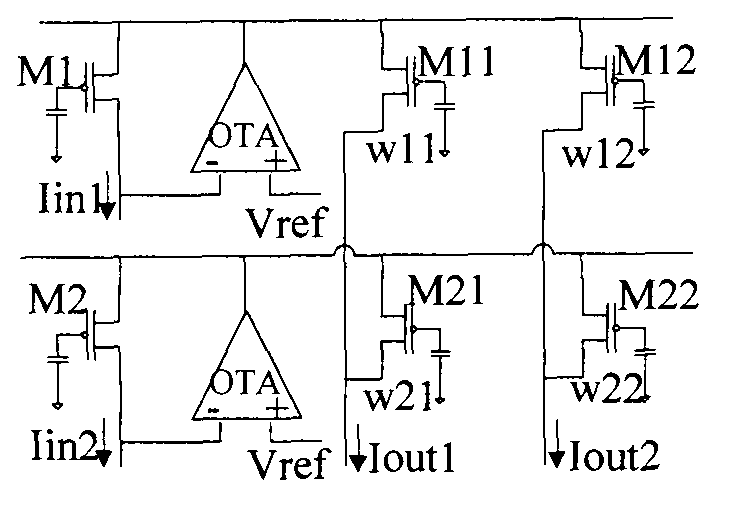

[0021] figure 1 It is a 2×2 (m=n=2) analog vector-matrix multiplier circuit, the input vect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com