Delay control circuit applied to memory unit and static random access memory

A technology of delay control and level control, applied in the field of circuits, can solve the problems of large area, high cost, complex circuit, etc., and achieve the effect of reducing discharge speed, small leakage current and realizing delay.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

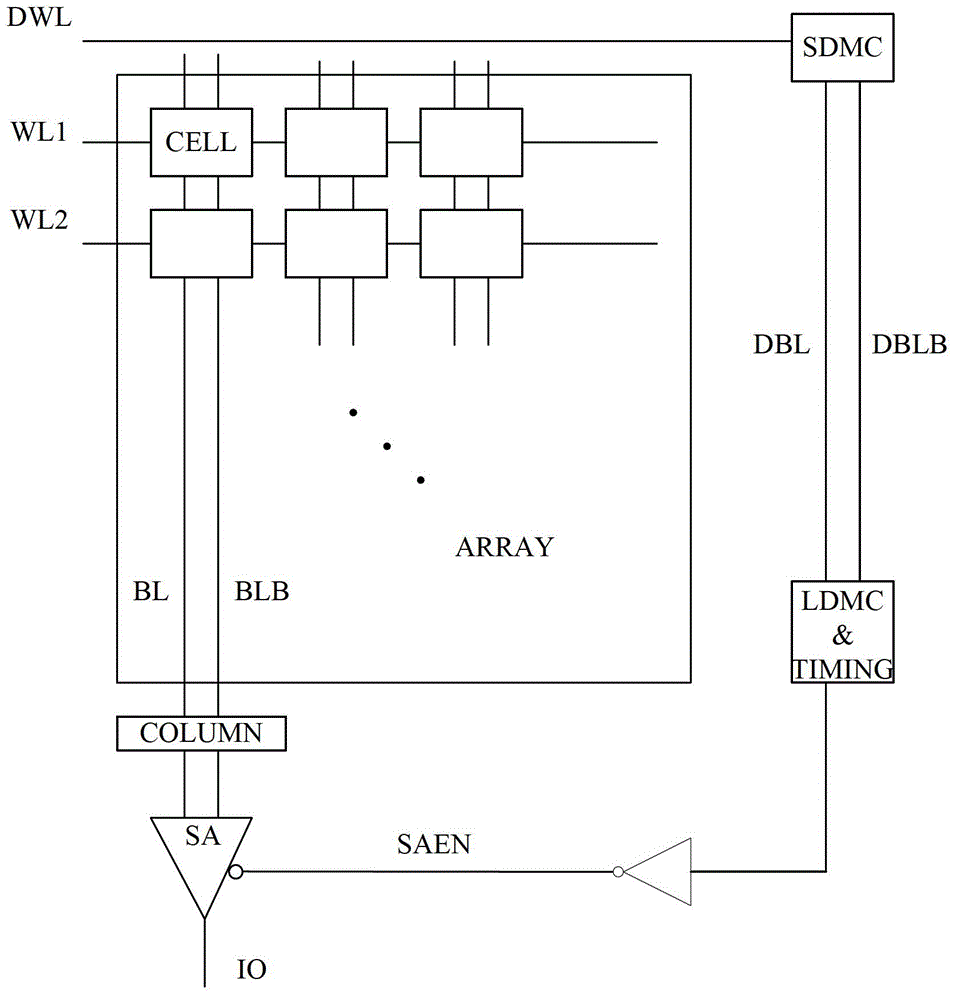

[0037] see Figure 4 , provides a circuit diagram of a delay control circuit applied to memory cells for the present invention, including: a control voltage divider circuit 101, a selection circuit 102, and a pull-down circuit 103, and the pull-down circuit includes a first NMOS transistor N0 and a second NMOS transistor pipe N1;

[0038] Wherein, the control voltage divider circuit 101 compares the virtual word line signal and the external control signal, and outputs the first control signal and the first control level VTHA, and the selection circuit 102 is used to receive the first control signal, and according to the The first control signal outputs a second control level VTHB, wherein the first control level VTHA controls the turn-on and turn-off of the second NMOS transistor, and the second control level VTHB controls the first NMOS transistor When the voltage Vcc is greater than the first preset value, the first NMOS transistor and the second NMOS transistor work in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com