Shift register, gate drive circuit and display apparatus

A gate drive circuit and shift register technology, applied in static memory, digital memory information, instruments, etc., can solve the problems of reducing circuit reliability, increasing power consumption, and high cost, so as to avoid threshold voltage drift and reduce individual Number, the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

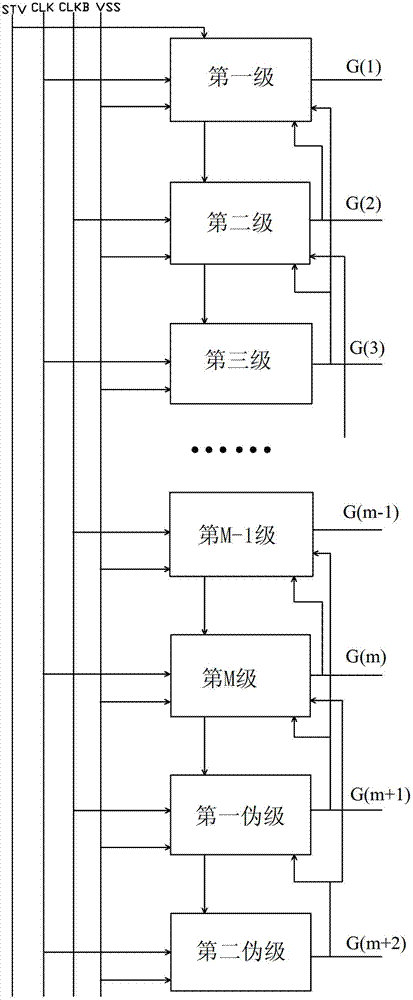

[0043] This embodiment describes a shift register, which is applied to a display substrate gate drive circuit. The shift register has cascaded M stages, and the Nth stage of the shift register includes:

[0044] The pull-up module outputs a driving signal to the output terminal of the Nth stage according to the input signal and the clock signal of the Nth stage;

[0045] A reset module, outputting a cutoff signal to the output terminal of the Nth stage according to the reset signal of the Nth stage;

[0046] The pull-down module maintains the output signal of the output terminal of the Nth stage as the cut-off signal according to the hold signal of the Nth stage;

[0047] Where N and M are natural numbers, and N is less than or equal to M;

[0048] When N is less than M-1, the hold signal of the Nth stage is the output signal of the output terminal of the N+2th stage;

[0049] The shift register also includes sequentially cascaded after the Mth stage:

[0050] The first dum...

Embodiment 2

[0053] This embodiment includes the whole content of embodiment one, but more specifically:

[0054] When N is 1, the input signal of the Nth stage is a field synchronization signal; when N is not 1, the input signal of the Nth stage is the output signal of the output terminal of the N-1th stage.

[0055] When N is less than M, the reset signal of the Nth stage is the output signal of the output terminal of the N+1th stage; when N=M, the reset signal of the Nth stage is the output signal of the first dummy stage.

[0056] In this embodiment, the first dummy stage and the second dummy stage can be reset by design methods such as using a vertical start pulse (STV) or an inverter.

[0057] In this embodiment, there is no need to use other signal generating devices, but the output signals of the upper stage and the lower stage are respectively used as the input signal, reset signal and hold signal of the current stage, which makes the circuit structure simpler.

Embodiment 3

[0059] This embodiment includes the whole content of embodiment two, but more specifically:

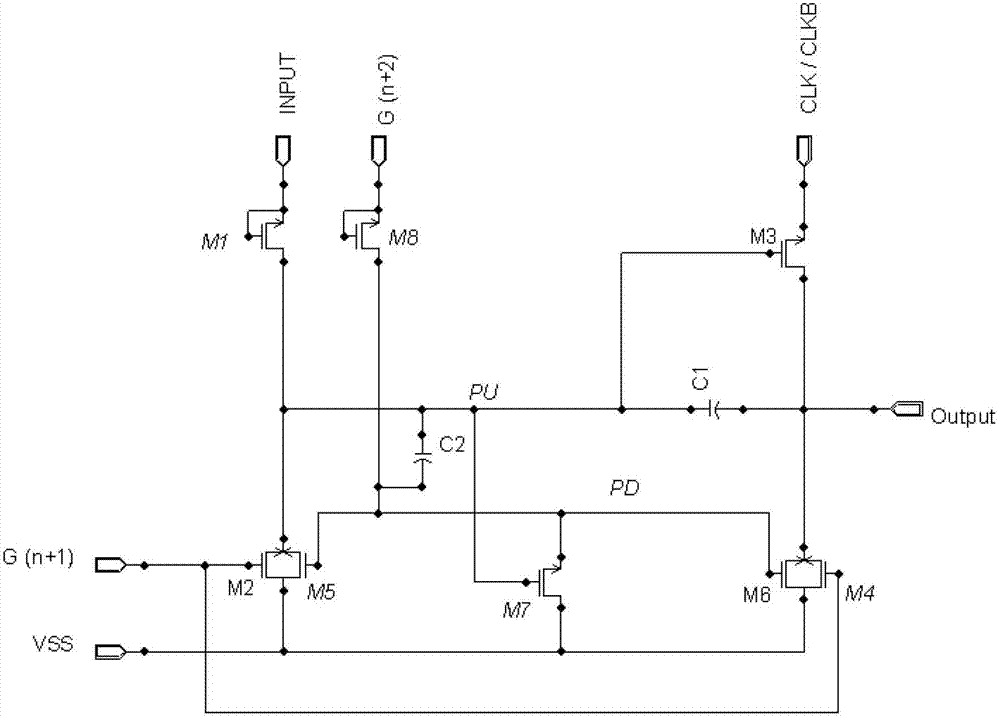

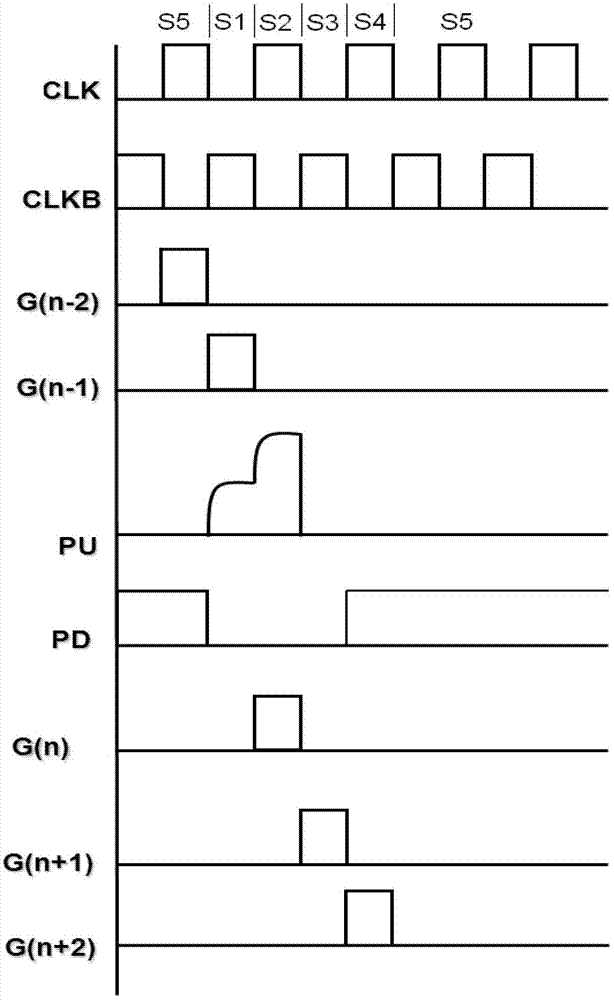

[0060] Such as figure 1 and figure 2 As shown, in this example:

[0061] The pull-up module includes a first transistor M1, a third transistor M3 and a first capacitor C1, wherein:

[0062] The gate and drain of the first transistor M1 (in the embodiment of the present invention, the source and drain of each transistor can be used interchangeably) are connected to the input signal, and the source is connected to the first node PU;

[0063]The gate of the third transistor M3 is connected to the first node PU, the drain is connected to the clock signal, and the source is connected to the output terminal Output;

[0064] The first capacitor C1 is connected between the first node PU and the output terminal Output.

[0065] The reset module includes a second transistor M2 and a fourth transistor M4, wherein:

[0066] The gate of the second transistor M2 is connected to the reset sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com