Identification and mitigation of hard errors in memory systems

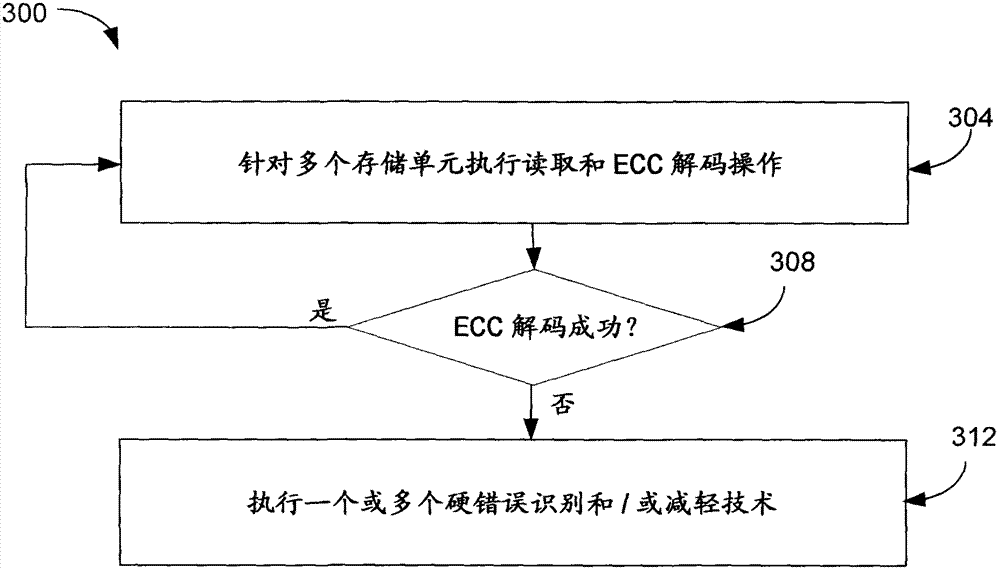

A technology of memory and storage unit, applied in the field of hard errors, which can solve the problems of soft decoding algorithm performance and hard error rate deterioration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

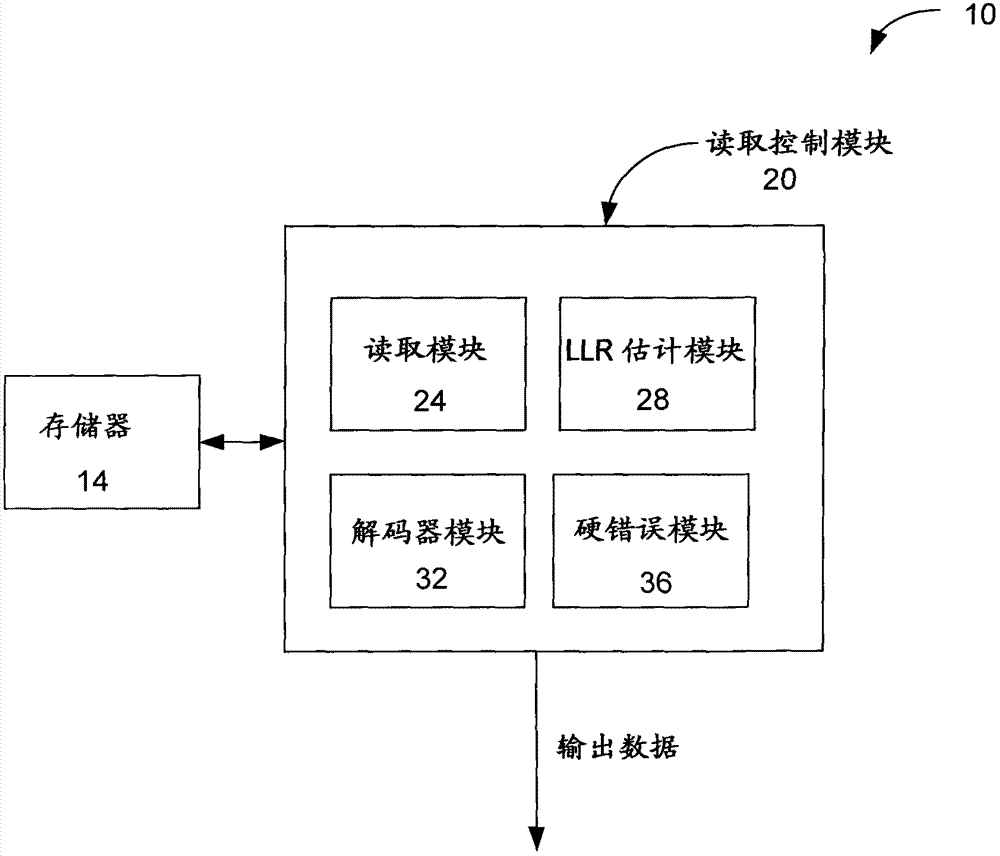

[0021] figure 1 An example of memory system 10 is schematically illustrated. Memory system 10 includes memory 14 . Memory 14 is any suitable type of memory, for example, volatile memory (eg, random access memory of a suitable type), non-volatile memory (eg, read-only memory), or the like. In an embodiment, memory 14 is an electrically erasable programmable read-only memory (EEPROM), such as flash memory.

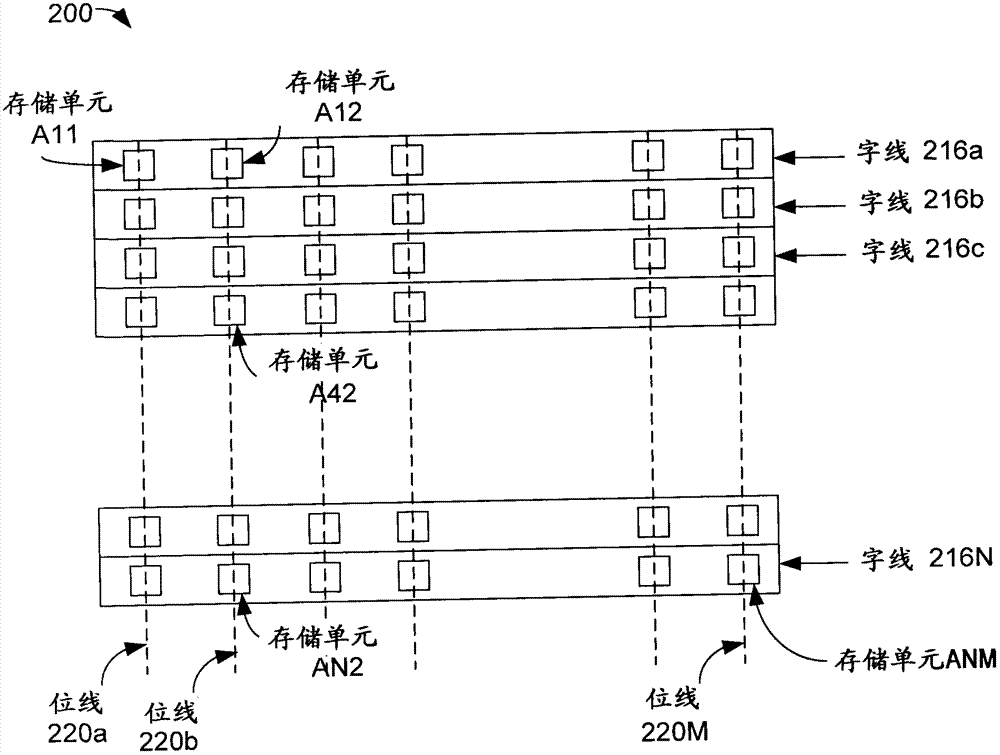

[0022] Although in figure 1 Not shown, the memory 14 includes a plurality of storage blocks, wherein each storage block includes a plurality of storage units, and each storage unit stores one or more bits of data. For example, each memory cell of memory 14 may be a single-level cell (SLC), which stores a single bit of data. In another example, each memory cell of memory 14 may be a multi-level cell (MLC), which stores multiple bits of data.

[0023] The memory system 10 includes a read control module 20 that includes a read module 24 , an LLR estimation module 28 , a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com