Structure for measuring bump resistance and package substrate comprising the same

A technology for measuring resistance and packaging substrates, which is applied to measuring devices, measuring electricity, measuring electrical variables, etc., can solve problems such as being unfavorable for reliability inspection at the design level, having no obvious help in reliability analysis, and being unable to observe multiple solder joints. Achieve the effect of improving reliability analysis efficiency, reducing time, and reducing the difficulty of positioning

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

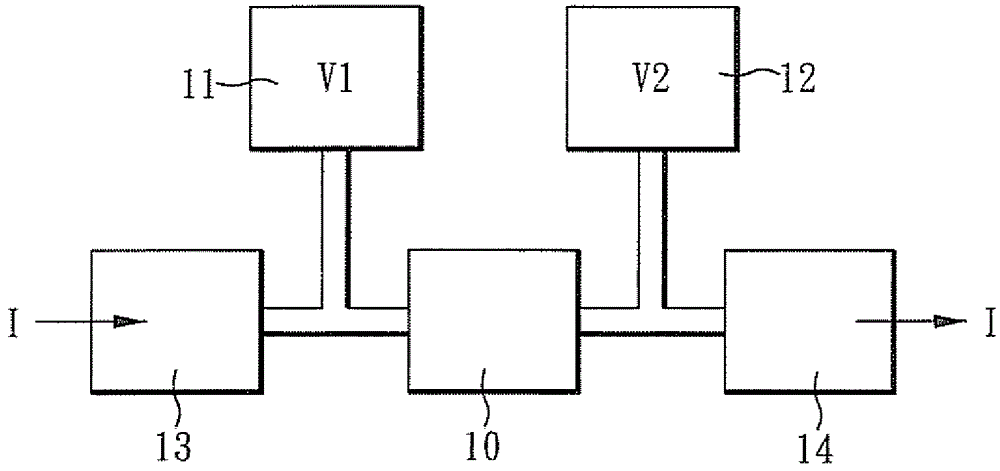

[0039]Such as Figure 4 As shown, it is a schematic connection diagram of the resistance measurement structure of the bump contact in this embodiment, including: the first to fifth solder bumps B1-B5, arranged in a line; the first connection pads C1, C3, C5; And the second connection pads C2, C4, C6; the first solder bump B1 and the second solder bump B2 are electrically connected by the first connection pad C1, and the second solder bump B2 is connected to the third solder bump B2 The bump B3 is electrically connected with the second connection pad C2, the first connection pad C1 is connected with a first voltage measurement pad P1; the second connection pad C2 is connected with an auxiliary connection pad P2', and the auxiliary connection pad P2' is connected with An auxiliary bump B2' is connected, and a second voltage measuring pad P2 is connected to the auxiliary bump B2'.

[0040] The third solder bump B3 and the fourth solder bump B4 are electrically connected by the f...

Embodiment 2

[0050] Such as Figure 5 As shown, it is a schematic diagram of the electrical connection of the resistance measurement structure of the bump contact of the packaging substrate of the present embodiment, and Figure 6 yes Figure 5 Sectional view of midline X-X'. Please also see Figure 5 and 6 , in this example, such as Figure 5 As shown, the auxiliary bumps B2', B4', the first voltage measurement pads P1, P3, and the second voltage measurement pads P2, P4 are located on the same side of the first to fifth solder bumps B1-B5. The first connection pads C1, C3, the first voltage measurement pads P1, P3, and the second voltage measurement pads P2, P4 are located on the printed circuit board 31 (such as Figure 6 shown), the second connection pads C2, C4 are located on the semiconductor chip 32 (such as Figure 6 shown) surface. The solder bumps B1-B5 are disposed between the first connection pad and the second connection pad.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com