Idle state test method of system-on-chip (SoC), system and test device

An idle state and test method technology, applied in the embedded field, can solve problems such as increased data processing by the test system, continuous testing of multiple test cases, and reduced test efficiency of the test system, achieving the effect of improving test efficiency and reducing processing capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0037] In the embodiment of the present invention, all test cases that SoC chips enter / exit idle state are stored in random access storage, and the one-to-one correspondence between the identification number and all test cases is established, and the test cases are executed in the SoC chip startup process. , until all the test cases of all SoC chips entering / exiting the idle state are tested.

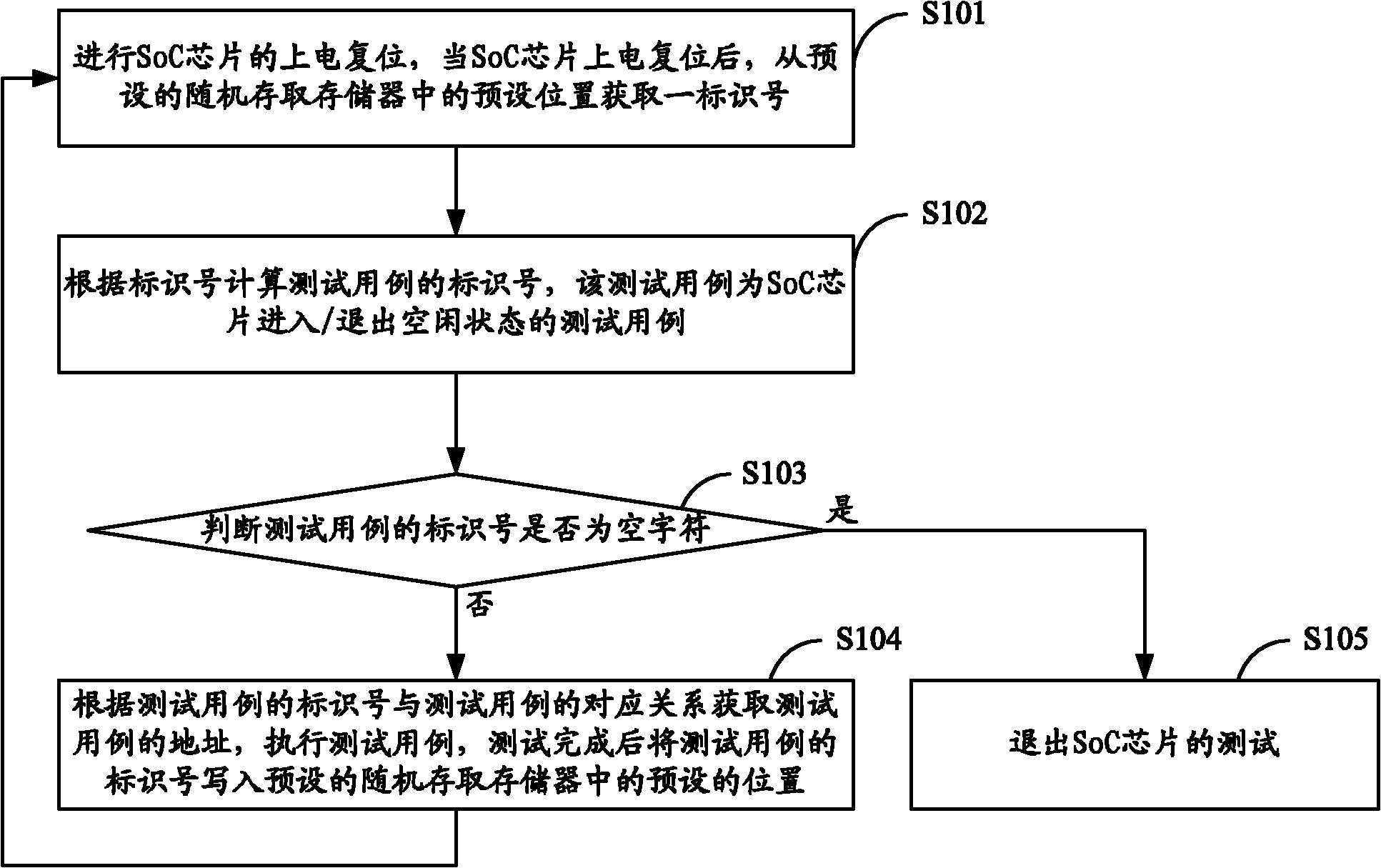

[0038] figure 1 The implementation flow of the idle state test method of the SoC chip provided by the first embodiment of the present invention is shown, and the details are as follows:

[0039] In step S101 , the power-on reset of the SoC chip is performed. After the power-on reset of the SoC chip, an identification number is obtained from a preset location in a preset random access memory.

[0040]SoC chip is a system-level chip with certain functions, which can include control logic module, microprocessor / microcontroller CPU core module, digital signal processor DSP module, embedded...

Embodiment 2

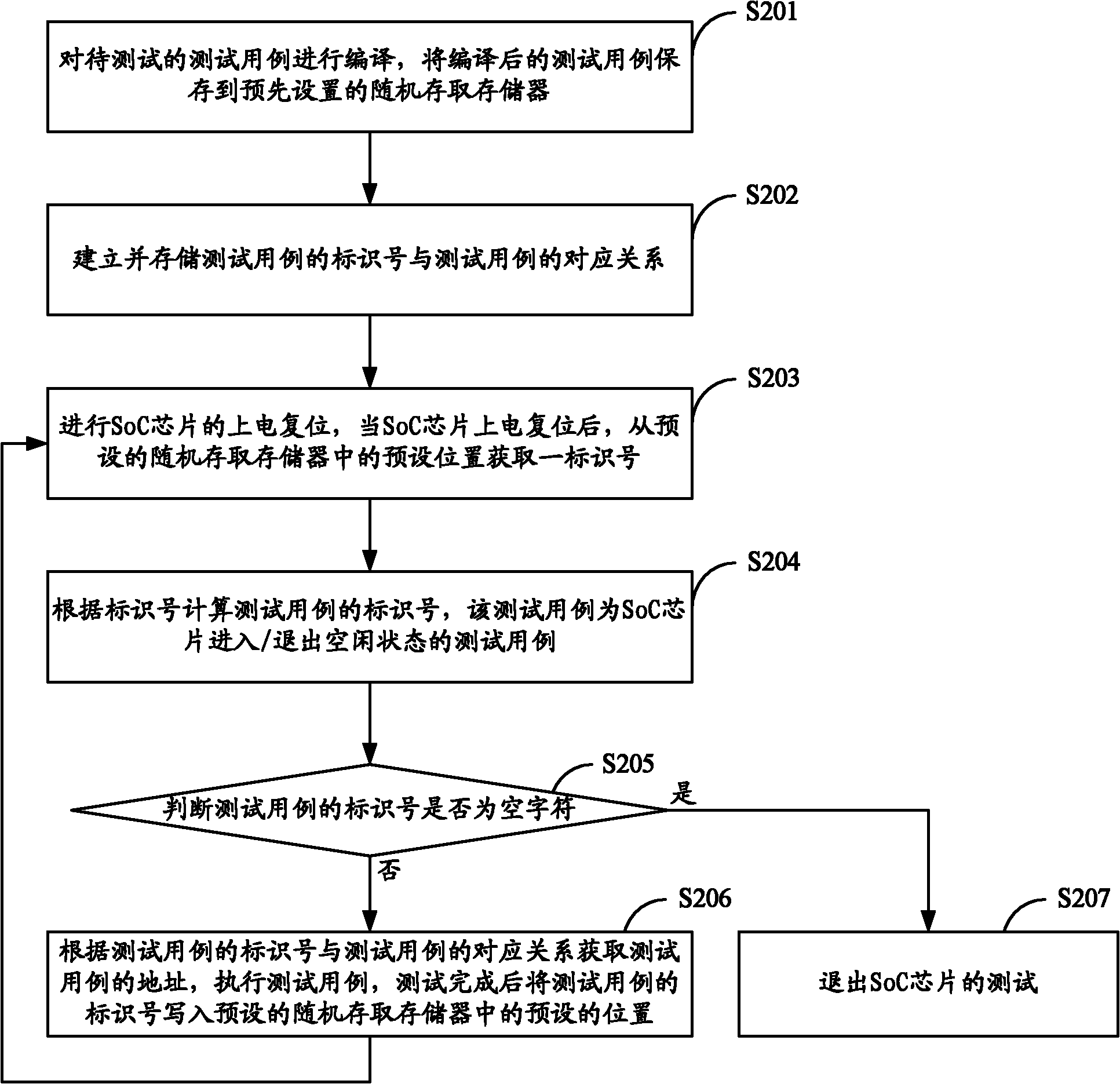

[0050] figure 2 The implementation process of the idle state test method of the SoC chip provided by the second embodiment of the present invention is shown, and the details are as follows:

[0051] In step S201, the test case to be tested is compiled, and the compiled test case is saved to a preset random access memory.

[0052] In the embodiment of the present invention, the test case to be tested is compiled in advance, and the compiled test case is saved to a preset random access memory, thereby improving the test efficiency of the test system.

[0053] In step S202, establish and store the correspondence between the identification number of the test case and the test case.

[0054] In step S203, the power-on reset of the SoC chip is performed. After the power-on reset of the SoC chip, an identification number is obtained from a preset location in a preset random access memory.

[0055] SoC chip is a system-level chip with certain functions, which can include control lo...

Embodiment 3

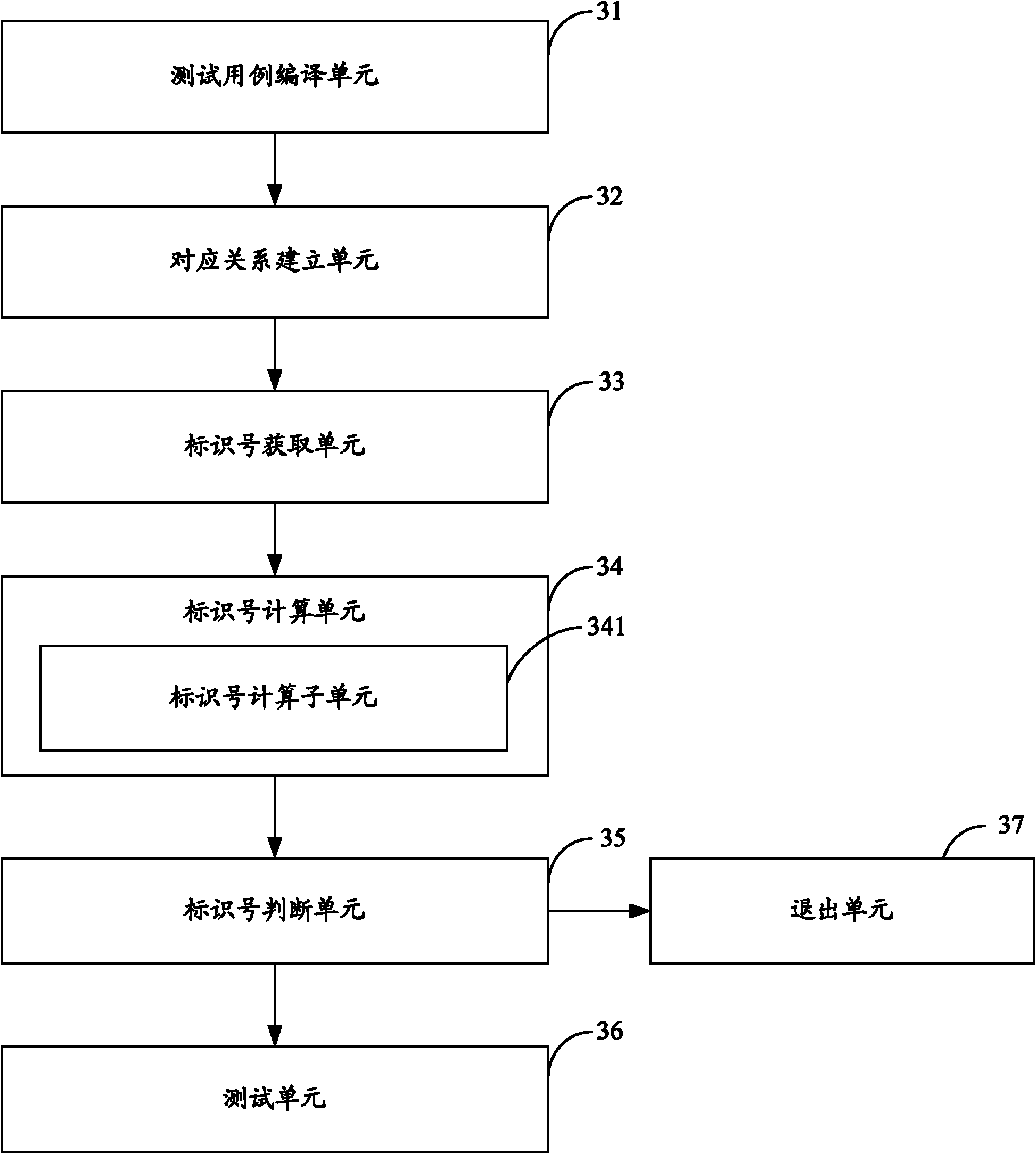

[0064] image 3 The structure of the idle state testing system of the SoC chip provided by the third embodiment of the present invention is shown, and for the convenience of description, only the parts related to the embodiment of the present invention are shown.

[0065] The idle state test system of this SoC chip can be used in the test platform of the idle state function of testing SoC chip, or in the SoC test device with the idle state test of SoC chip, can be the software unit that runs in these SoC test devices, It can also be integrated into these SoC test devices as an independent pendant or run in the application systems of these SoC test devices, wherein:

[0066] The test case compiling unit 31 compiles the test case to be tested, and saves the compiled test case to a preset random access memory.

[0067] In the embodiment of the present invention, the test case to be tested is compiled in advance, and the compiled test case is saved to a preset random access memor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com