Optimization method of SoC (System on Chip) address mapping

An optimization method and address technology, applied to instruments, electrical digital data processing, etc., can solve problems such as low efficiency of SoC address mapping, reduced circuit area, and reduced frequency of use of asynchronous FIFOs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

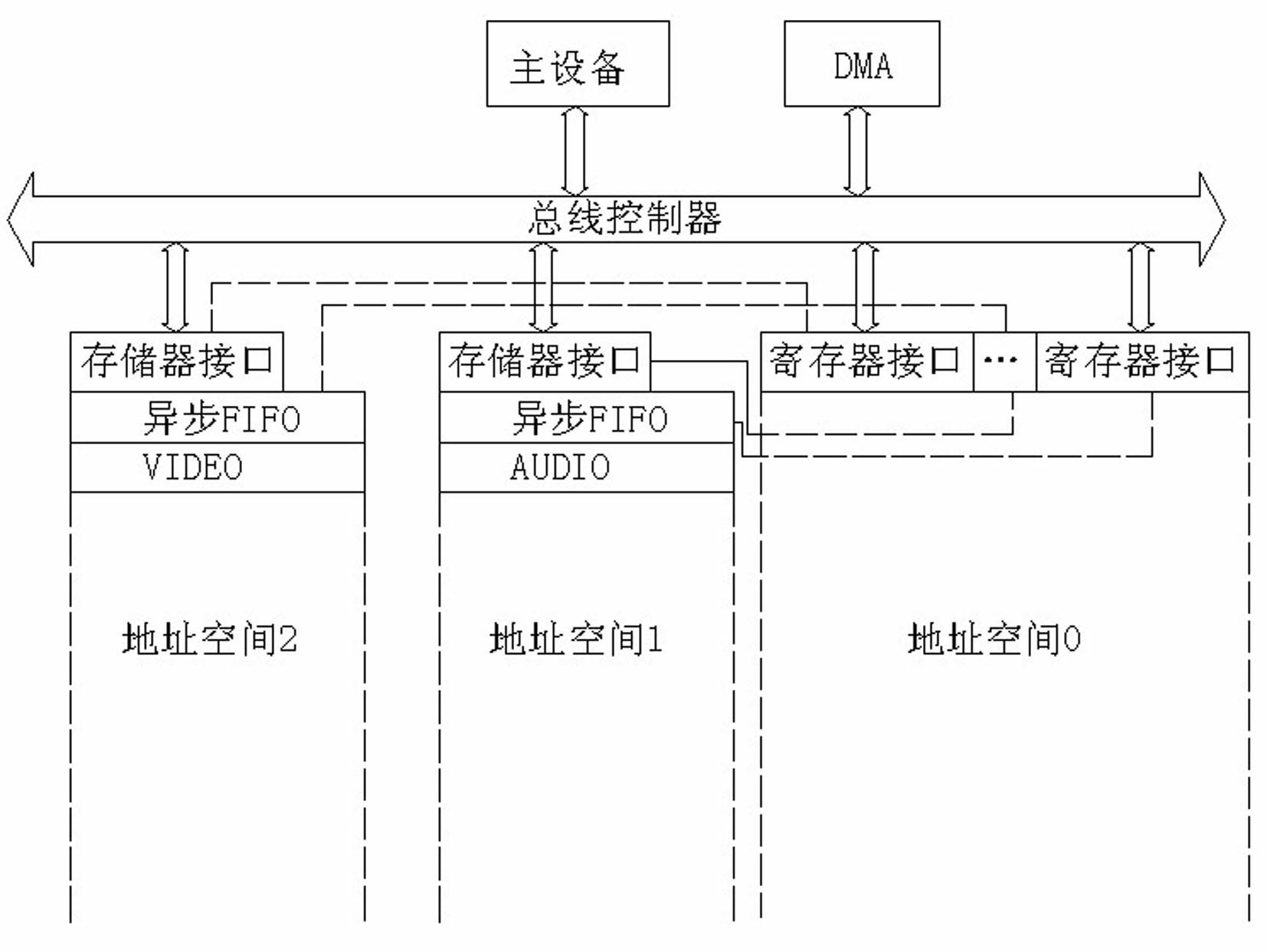

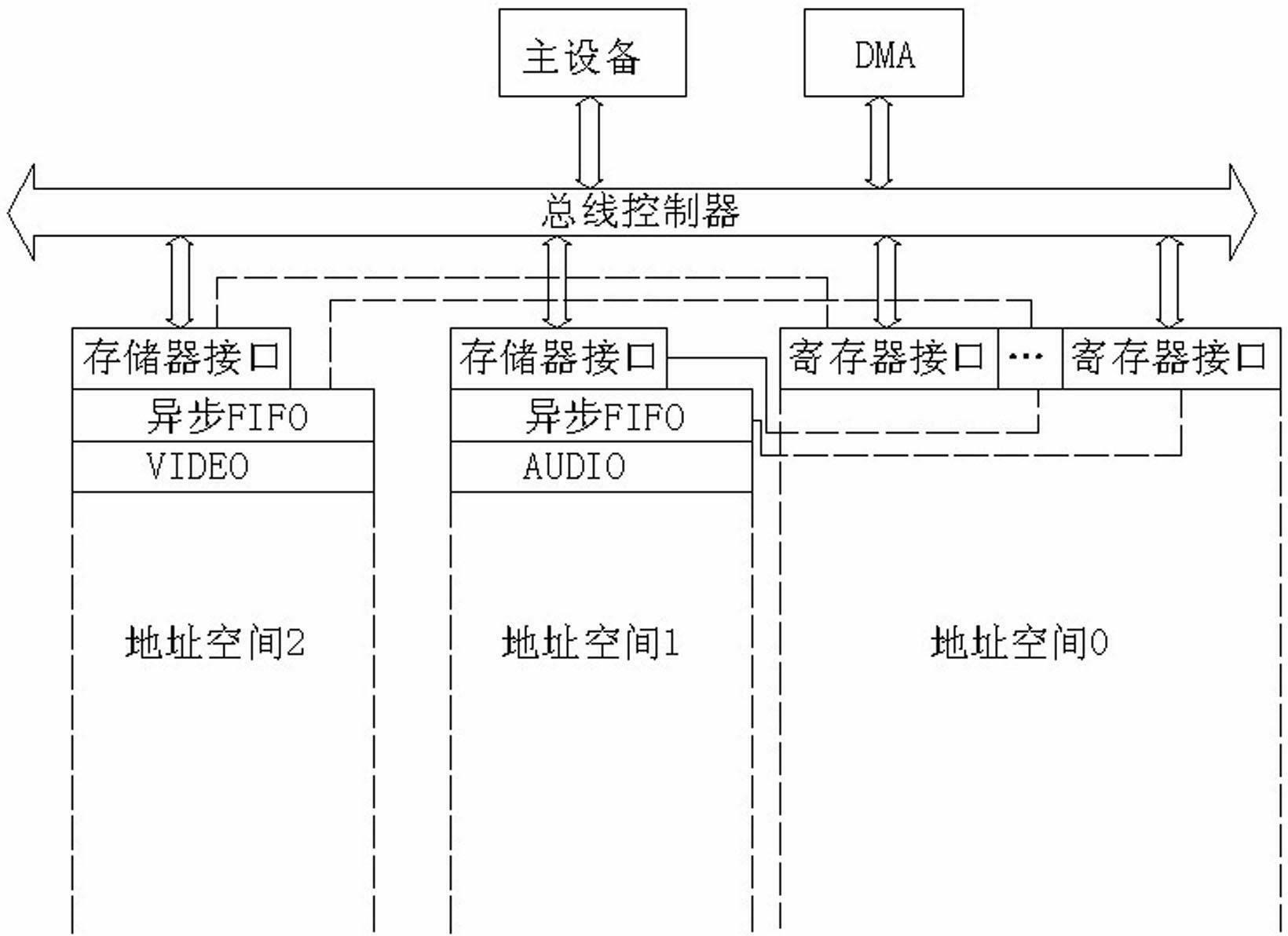

[0017] Refer to the attached figure 1 , the current common SoC address mapping method is that each slave device has an independent address port, combined with software, the hardware register group is allocated to another address space as a single device. In contrast, an embodiment according to the present invention presents figure 2 In this method, the existing address allocation method is maintained, that is to say, each slave device is mapped to two entry addresses, which are uniformly pushed into the CPU / DSP address stack, so that the CPU / DSP can find the corresponding function module. At the same time, the hardware Above, the register interface is implemented into the corresponding hardware module, and it is more accurately expressed as implemented into the memory interface. Under such configuration conditions, in terms of hardware architecture, it can be understood that each slave device corresponds to two address spaces.

[0018] Such as figure 2 As shown, the bus c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com