Structured mixed bit-width multiplying method and structured mixed bit-width multiplying device

A multiplication and structuring technology, applied in the field of realizing structured mixed bit-width multiplication, can solve problems such as time-consuming, and achieve the effects of high area utilization, regular layout, and high utilization of hardware resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

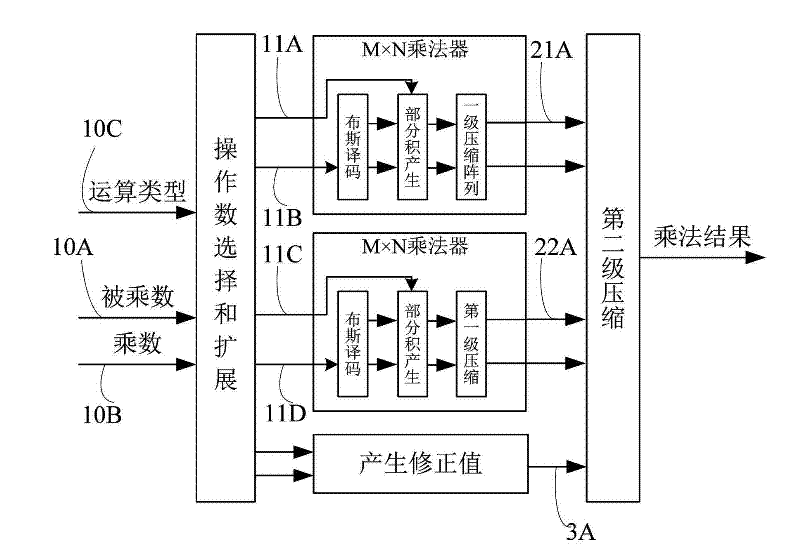

[0034] Such as figure 1 As shown, the implementation steps of the structured mixed bit width multiplication method in this embodiment are as follows:

[0035] 1) Input multiplier, multiplicand and operation control signal including operation type and sign bit;

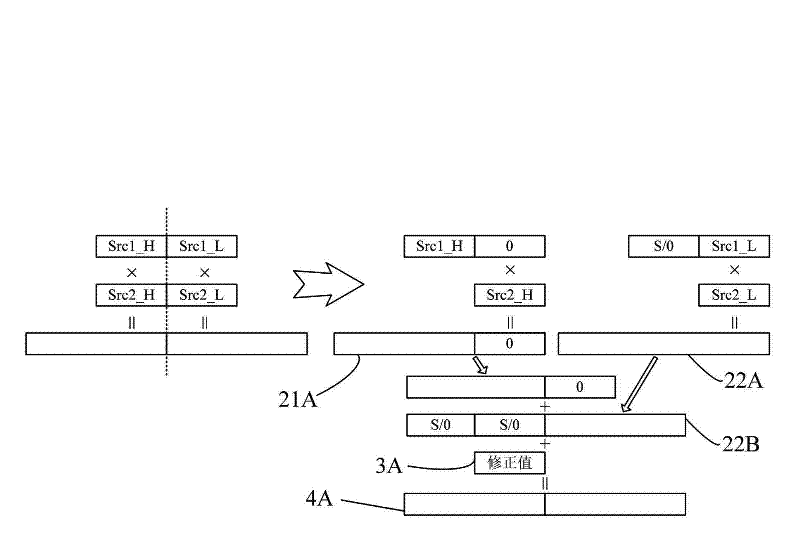

[0036]2) Split the multiplier and multiplicand according to the operation type, and extend the sign bit of the split multiplicand according to the sign bit;

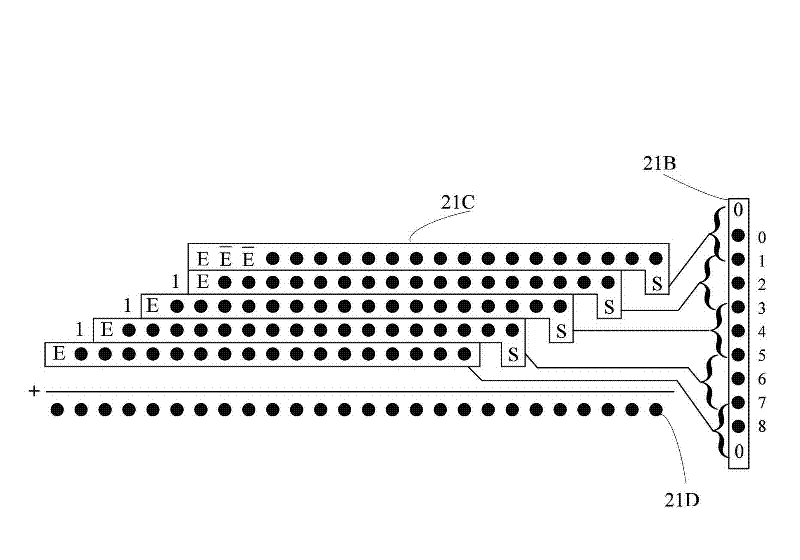

[0037] 3) Send the multiplier and multiplicand after splitting and sign bit extension to two M×N multipliers for Booth decoding and partial product generation, and the partial products generated by all M×N multipliers are respectively to compress;

[0038] 4) Generate a correction value according to the operation type and sign bit in the operation control signal;

[0039] 5) Compress all the output results obtained in step 3) and the correction value obtained in step 4) to obtain the multiplication result.

[0040] This embodiment includes two compression pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com