Flash memory unit forming method

A flash memory cell and substrate surface technology, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of flash memory cell double peak effect, reverse narrow channel effect, transistor cycle durability and so on, so as to avoid double peak effect, improved cycle durability, and uniform thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

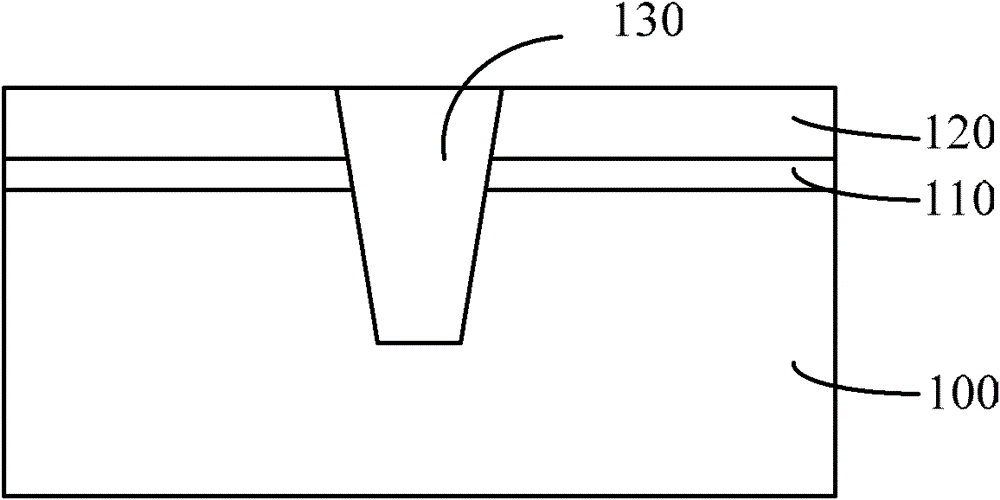

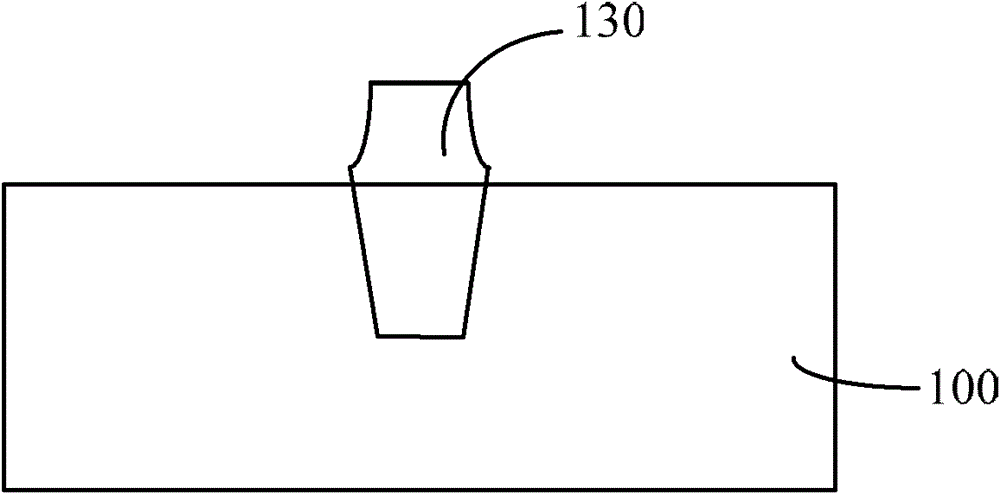

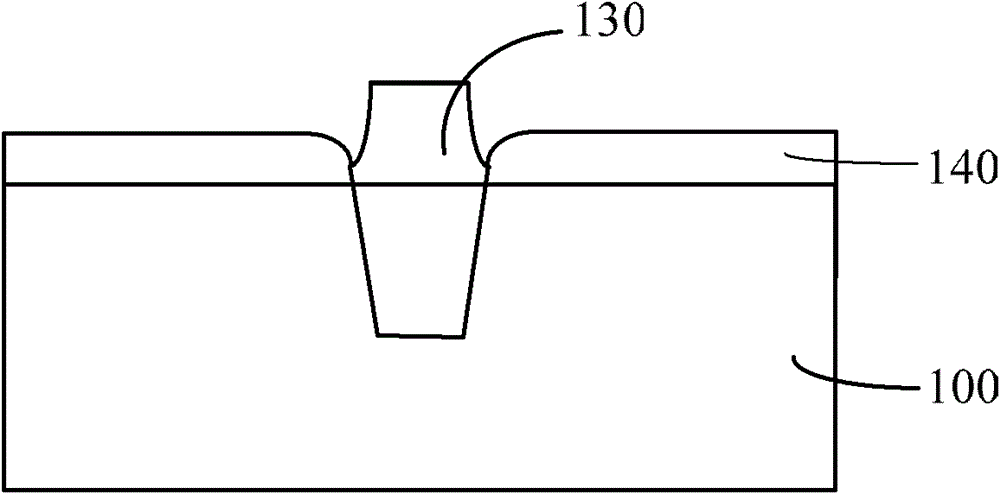

[0028] It can be known from the background technology that the flash memory cell formed by the existing flash memory cell forming method will produce a double peak effect and an inverse narrow channel effect, and the cycle durability of the flash memory cell is relatively poor. The inventors of the present invention have studied the above problems and tried to solve the above problems by adjusting the parameters of each step, but the results were very little. Therefore, the inventor further adjusted the process and found that the tunneling oxide was formed by a chemical vapor deposition process. Layer can solve the above problems.

[0029] According to the inventor's experimental research, a method for forming a flash memory cell is provided in the present invention. The method for forming a flash memory unit provided by the present invention includes: providing a substrate; forming a tunnel oxide layer on the surface of the substrate using a chemical vapor deposition method; and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com