Software fault-tolerant method capable of comprehensively on-line self-detection single event upset

A single-event flipping, software fault-tolerant technology, applied in the generation of response errors, instruments, electrical and digital data processing, etc., to save hardware costs and time costs, improve efficiency, and count the number of single-event flips in a comprehensive manner.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] The following is a specific implementation description by using more DSP 6X series processors.

[0065] 1. Perform memory address link configuration

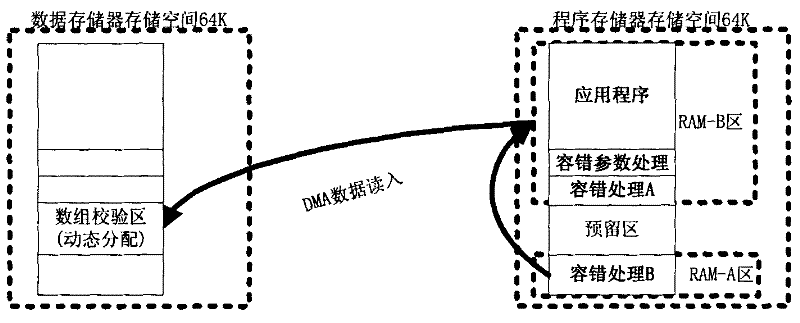

[0066] After the DSP processor chip is reset, according to the memory mapping relationship, the ROM loading mode is adopted to move all the codes in the ROM space to the address of the program memory space through the processor chip. As shown in the accompanying drawings figure 1 shown.

[0067] The corresponding situation of the load address segment: ROM_B area places the program code including all application programs, and the program code of the fault-tolerant processing parameter generation module and the fault-tolerant processing A module. When the program is running, it is loaded in the corresponding program memory RAM_B area; The program code of the B module is loaded into the corresponding program memory RAM_A area when the program is running, and the ROM_B area and ROM_A area are determined according to the siz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com