Vector dot product accumulating network supporting reconfigurable fixed floating point and configurable vector length

A vector length, fixed-floating-point technology, applied in the field of high-performance digital signal processors, can solve problems such as difficult programming, low flexibility, and low hardware utilization, and achieve improved code density, high computing performance, and simplified complexity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

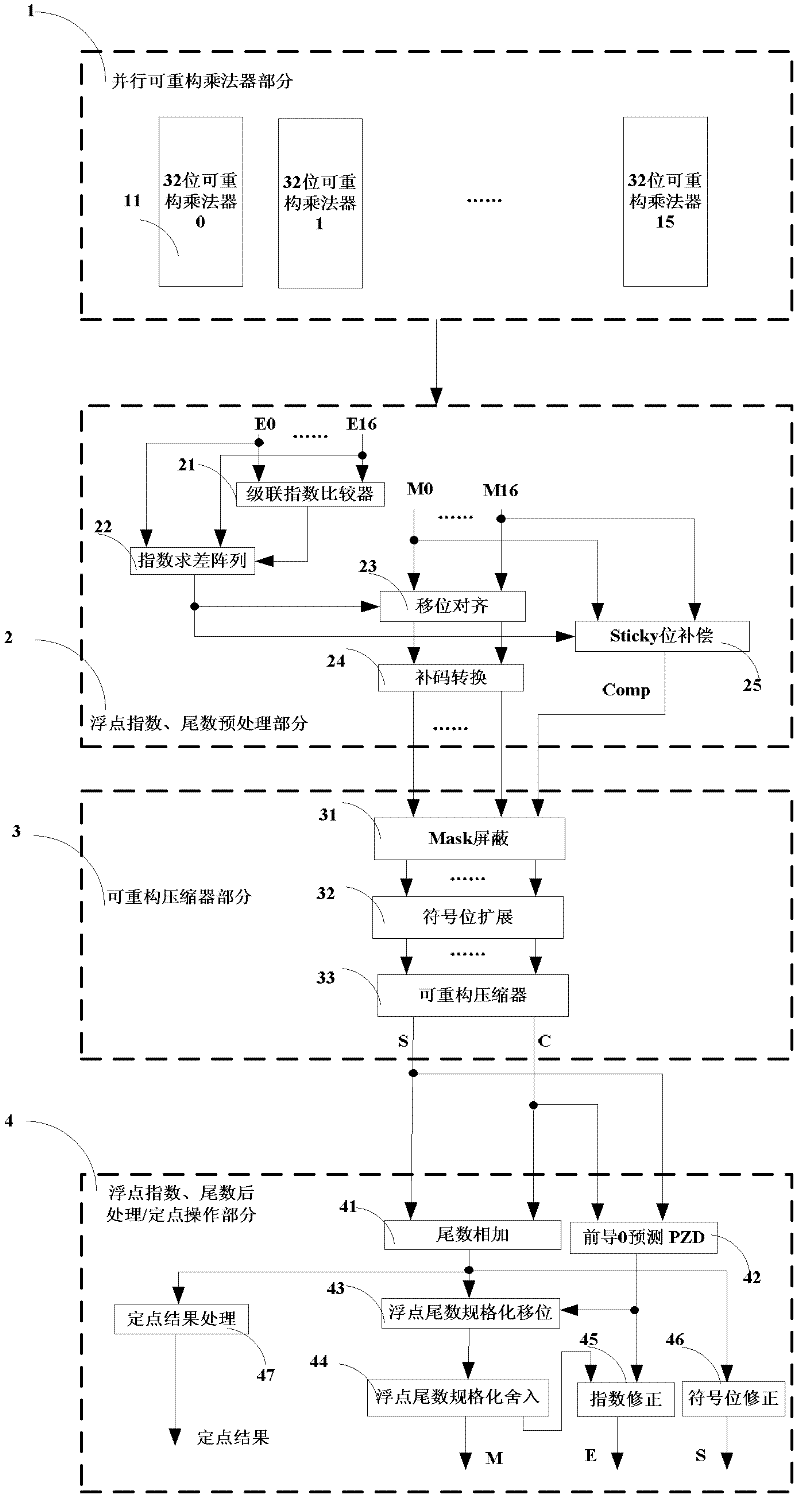

[0026] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

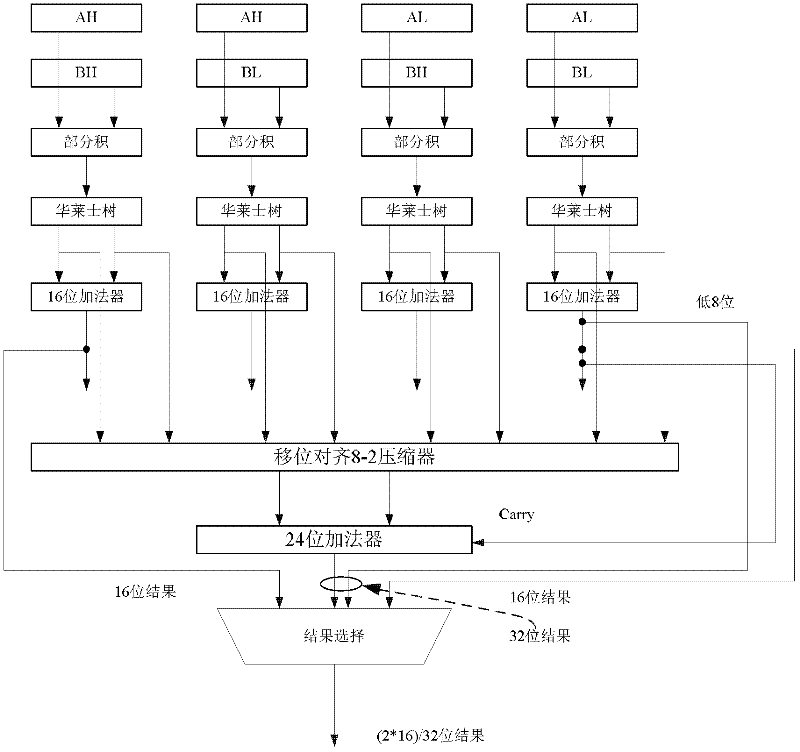

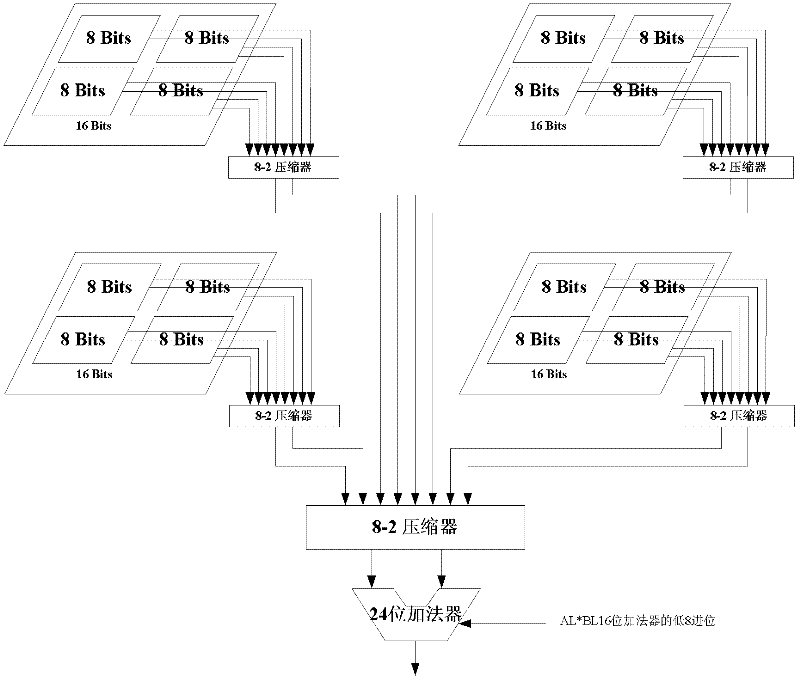

[0027] The main features of the invention are: the data format can be reconfigured, and the vector length can be configured. The following description symbols are agreed during the description process: the dot product instruction is described as D=A+B DOTC{(U)}{(M)}{(FBS)}; where A and D are 32-bit scalar data, and B and C are 512-bit vector data, DOT means the dot product operator; Mask is a 64-bit register, each bit controls the 8-bit byte of the B×C result; M means that the vector point accumulation operation is affected by the Mask register, when the M option does not exist Indicates that the Mask register has no effect on the vector point accumulation operation; U indicates the unsigned option; FBS indicates the data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com