LCD (liquid crystal display) driving device and driving method

A liquid crystal display and driving device technology, applied to static indicators, instruments, etc., can solve the problems of complex wiring, large number of wiring, and high production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

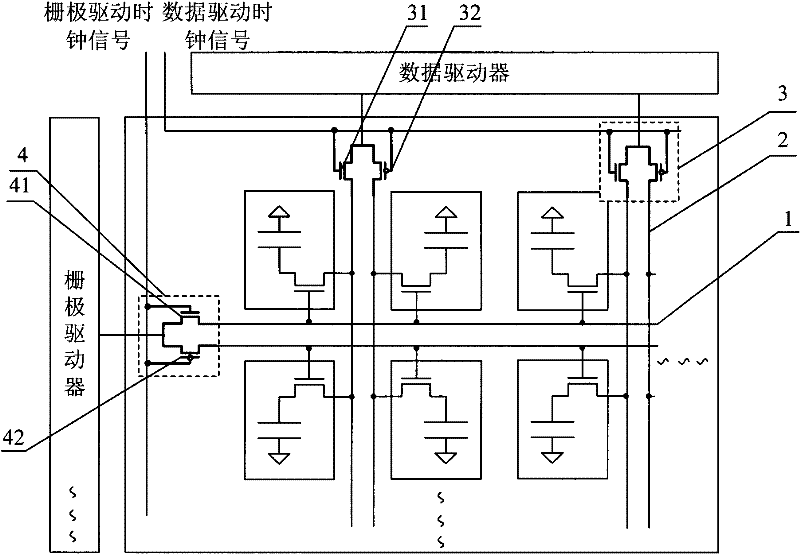

[0062] In this embodiment, the scheme of setting up an array of gate line driving modules and an array of data line driving modules is adopted, and further, the two gate lines connected to the gate line driving module are one odd-numbered row gate line and one even-numbered row Row gate lines; the two data lines connected to the data line driving module are an odd-numbered column data line and an even-numbered column data line.

[0063] Specifically, the gate line driving module 4 used includes: a high-level active first thin film transistor 41 and a low-level active second thin film transistor 42, wherein the gate of the first thin film transistor 41 and the data line drive clock signal The output terminal of the second thin film transistor 42 is connected to an output channel of the gate driver, and its drain is connected to an odd-numbered gate line 1; the gate of the second thin film transistor 42 is connected to the gate line drive clock signal connected to the output ter...

Embodiment 2

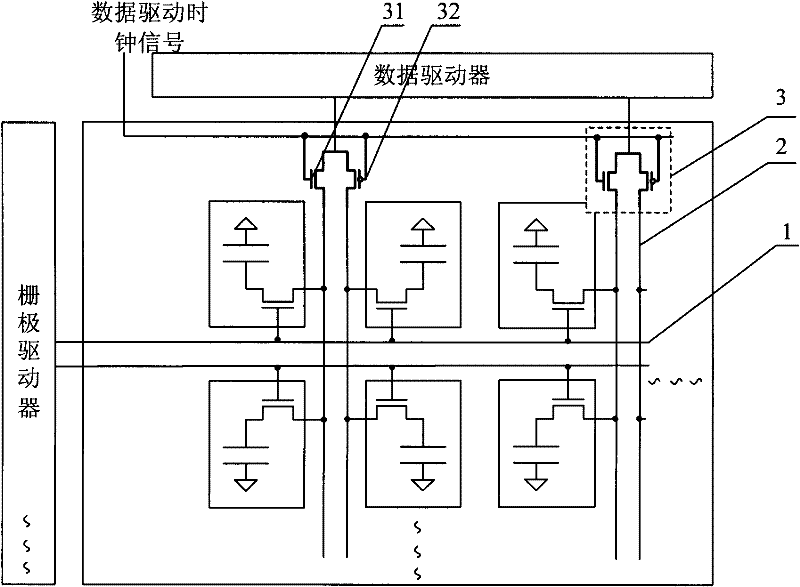

[0075] In this embodiment, only the array of data line driving modules is adopted, and further, the two data lines connected to the data line driving modules are one odd-numbered column data line and one even-numbered column data line.

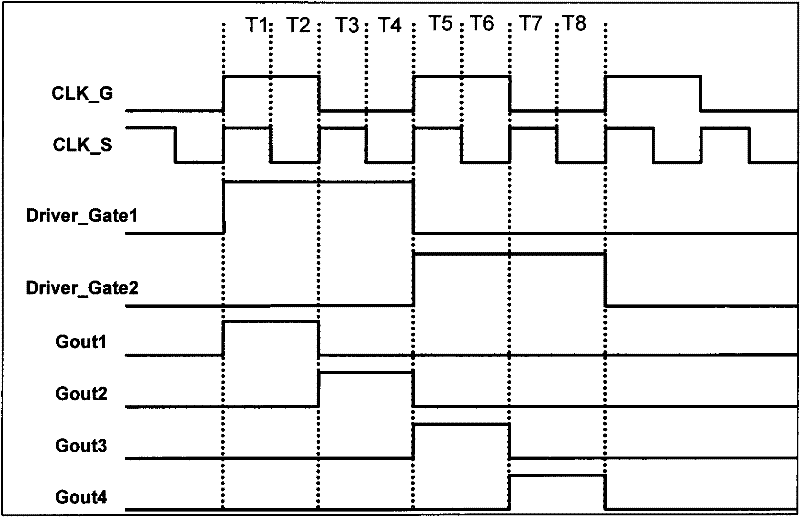

[0076] Specifically, such as Figure 4 As shown, it is the driving timing diagram of Embodiment 2 of the present invention, wherein CLK-S represents the data line driving clock signal, Driver-Gate1 represents the output of the first output channel of the gate drive IC, and Driver-Gate2 represents the gate drive IC The output of the second output channel, Gout1 represents the output of the first row of gate lines, Gout2 represents the output of the second row of gate lines, Gout3 represents the output of the third row of gate lines, and Gout4 represents the output of the fourth row of gate lines.

[0077] Specifically, such as image 3 and Figure 4as shown,

[0078] 1) During the T1 and T2 periods, the first output channel Driver_Date1 of t...

Embodiment 3

[0083] In this embodiment, only the gate line driving module array is adopted, and further, the two gate lines connected to the gate line driving module are one odd-numbered row gate line and one even-numbered row gate line.

[0084] Specifically, such as Figure 6 As shown, it is the driving timing diagram of Embodiment 3 of the present invention, wherein CLK-G represents the gate line drive clock signal, Driver-Gate1 represents the output of the first output channel of the gate drive IC, and Gout1 represents the gate line of the first row Output, Gout2 represents the output of the gate line of the second row, Gout3 represents the output of the gate line of the third row, and Gout4 represents the output of the gate line of the fourth row.

[0085] Specifically, such as Figure 5 and Figure 6 As shown, when the first output channel Driver_Date1 of the gate driver IC outputs a high level:

[0086] 1) During the T1 time period, CLK_G is at a high level, the first thin film t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com